# Nanometer CMOS Clocked Storage Elements: Optimization Techniques, Comparison and Novel Energy-Efficient Design Solutions

# Elio Consoli

Ph.D. in Electronic, Automation and Control of Complex Systems

Engineering (XXIV cycle)

University of Catania, Italy

# Nanometer CMOS Clocked Storage Elements: Optimization Techniques, Comparison and Novel Energy-Efficient Design Solutions

# by Elio Consoli

B.S. (University of Catania, Italy) 2005 M.S. (University of Catania, Italy) 2008

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Electronic, Automation and Control of Complex Systems Engineering (XXIV cycle)

Dept. of Electrical, Electronic and Information Engineering Faculty of Engineering University of Catania, Catania, Italy

Coordinator:

Prof. Luigi Fortuna

Tutor:

Prof. Gaetano Palumbo

# To

(mom) Francesca (dad) Maurizio Laura Abstract V

### **ABSTRACT**

Clocked storage elements are among the most important elements in the design of digital systems, such as microprocessors, since they allow to synchronize and regulate the entire flow of digital data within the system.

With the aim of obtaining conspicuous performance increments at each process generation, dimensional scaling has been supported by the reduction of the number of logic stages within each pipeline stage. Therefore, an increasing impact of the timing overhead due to clocked storage elements on the clock period can be observed. Moreover, the continuous increase in energy consumption has become the major concern limiting the speed performances of VLSI integrated circuits, insomuch as, even for high-speed systems, designs undergo a power limited regime and the achievement of energy-efficiency becomes the primary target.

The topics of energy-efficient design, analysis, comparison and selection of suitable clocked storage elements topologies for applications in nanometer technologies have been the focus of the research activity carried out by the candidate in pursuit of the Ph.D. degree. The aim of this thesis is to provide a deep understanding of the challenges relative to clocked storage elements design and selection when including all the above mentioned aspects, as well as to propose novel energy-efficient solutions at the transistor- and microarchitectural design levels.

The basic theoretical foundations are provided to set the stage for the comprehension of analyses and results. Exhaustive methodologies are presented and many analytical derivations are included, since they allow to gain an insight on the main dependencies of relevant parameters on circuital properties. Finally, several results, which have been derived by carrying out extensive simulation analyses and measurements on an integrated chip prototype are reported to emphasize the practical perspective of the work.

Acknowledgements VII

### ACKNOWLEDGEMENTS

Firstly, I want to thank my Ph.D. supervisor, Prof. Gaetano Palumbo, and my research advisor, Prof. Massimo Alioto, for their technical and inspirational support. All the results achieved during my Ph.D. experience are shared with them and ensue from their technical teachings, constant motivation and invaluable guidance. Because of their wonderful human approach, which I am extremely grateful for, they are not only scientific tutors but also life mentors.

I wish to express my most sincere gratefulness to Prof. Salvatore Pennisi, Prof. Gianluca Giustolisi and Prof. Giuseppe Di Cataldo, whose human and cultural worthiness I admire. They have always provided me precious helpfulness and careful suggestions.

I would like to acknowledge the Ph.D. coordinator, Prof. Luigi Fortuna, for its motivating guide and all the other Professors, Researchers and Research Assistants at DIEEI, whose organizational skills have made attending my Ph.D. program a fruitful and exciting experience.

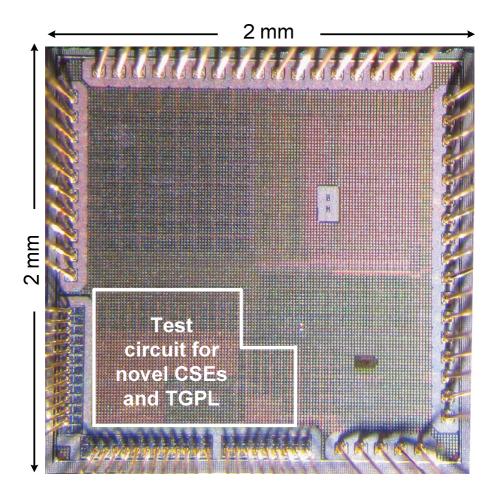

Part of my research activity has been carried out at the Berkeley Wireless Research Center, UC Berkeley, and hence I want to thank Prof. Jan Rabaey, all BWRC staff and, again, Prof. Massimo Alioto for giving me the wonderful opportunity to work in such an astonishing research environment. The collaboration with BWRC culminated in the realization of an integrated prototype and I thank STMicroelectronics for chip fabrication.

I am also grateful to my lab mates at DIEEI, Melita Pennisi, Dario Mita, Walter Aloisi and David Cristaldi for their enjoyable company. A special thank goes to Davide Marano for his sincere friendship.

I want to extend my thanks to all friends, relatives and colleagues, who have accompanied me throughout this three-year experience.

Finally, I am immensely grateful to my family.

VIII Acknowledgements

I wish to thank my sister for her support during hard working periods and for helping me to preserve my confidence and reference points when worrying about the choices for the future.

I will be endlessly indebted to my father, who has always supported me by any means. His experience and unconditional love have been the sources of indispensable suggestions, which have represented the strong and encouraging foundation for all the decisions that I have taken.

I can hardly express my gratitude to my mother, which my deepest thanks goes to. Her enormous and endless effort to sustain, encourage and make me live a fully happy life is undoubtedly the biggest gift I have ever received. I am who I am thanks to her infinite love and she will always be the main reference for any future achievement.

Least but not last, I want to thank my lovely fiancée Laura, who changed my life by giving me infinite joy and happiness. Day by day, Laura has made me know the real meaning of the word "love" and, while preparing my future next to her, I am truly conscious that she is the most important person in my life.

Table of Contents IX

# TABLE OF CONTENTS

| INTRODUCTION                                                | 1  |

|-------------------------------------------------------------|----|

| 1. THE LOGICAL EFFORT METHOD                                | 5  |

| 1.1 An RC Model for the Delay of Logic Gates                | 5  |

| 1.2 The Logical Effort Model                                | 8  |

| 1.3 Limitations of the Original Logical Effort Model        | 10 |

| 1.4 Basic Estimation of Logical Effort Parameters           | 13 |

| 1.5 Accurate Estimation of Parameters <i>g</i> and <i>p</i> | 16 |

| 1.5.1 Internal nodes capacitances                           | 16 |

| 1.5.2 Elmore delay                                          | 17 |

| 1.5.3 Parameters calibration                                | 19 |

| 1.5.4 Non-step input                                        | 21 |

| 1.6 Multistage Logic Networks and Delay Minimization        | 21 |

| 1.6.1 Path parameters                                       | 21 |

| 1.6.2 Optimized design                                      | 23 |

| 1.7 Optimum Number of Stages                                | 24 |

| 1.8 Extension of the Model to Non-Static Gates              | 26 |

| 1.8.1 Dynamic and Domino gates with keeper                  | 26 |

| 1.8.2 Logic with transmission-gates and pass-transistors    | 28 |

| 1.9 Nonlinearities and Need for Iterative Procedures        | 30 |

| A.1 Derivation of Logical Effort with a Current Approach    | 31 |

X Table of Contents

| 2. DESIGN IN THE ENERGY-DELAY SPACE                                                                                                                                                                                                                                                          | 33                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.1 Energy Modeling                                                                                                                                                                                                                                                                          | 33                                           |

| 2.2 Energy-Delay Space Analysis and Hardware Intensity                                                                                                                                                                                                                                       | 38                                           |

| 2.2.1 The energy-efficient curve                                                                                                                                                                                                                                                             | 38                                           |

| 2.2.2 Energy-delay metrics and hardware intensity                                                                                                                                                                                                                                            | 40                                           |

| 2.2.3 Voltage intensity and generalization of the sensitivity criterion                                                                                                                                                                                                                      | 42                                           |

| 2.3 Energy-Efficient Design of Digital Circuits                                                                                                                                                                                                                                              | 44                                           |

| 2.3.1 The role of the input capacitance                                                                                                                                                                                                                                                      | 44                                           |

| 2.3.2 Definition of design space bounds                                                                                                                                                                                                                                                      | 45                                           |

| 2.3.3 Simulations based optimization of small size circuits                                                                                                                                                                                                                                  | 49                                           |

| 2.3.4 Nonlinear and convex optimization of large size circuits                                                                                                                                                                                                                               | 51                                           |

| 2.4 Design of Energy-Efficient Pipelined Systems                                                                                                                                                                                                                                             | 54                                           |

| 2.4.1 Zyuban & Strenski's hardware-voltage intensity criteria                                                                                                                                                                                                                                | 55                                           |

| 2.4.2 Practical guidelines to design energy-efficient pipelines                                                                                                                                                                                                                              | 58                                           |

| A.2 Convex Optimization                                                                                                                                                                                                                                                                      | 62                                           |

| 2 CLOCKED CTODACE ELEMENTO                                                                                                                                                                                                                                                                   | <b>(</b>                                     |

| 3. CLOCKED STORAGE ELEMENTS                                                                                                                                                                                                                                                                  | <b>65</b>                                    |

| 3.1 Clocking in Synchronous Digital Systems                                                                                                                                                                                                                                                  |                                              |

|                                                                                                                                                                                                                                                                                              |                                              |

| 3.2 Features of the Clock Signal                                                                                                                                                                                                                                                             | 68                                           |

| 3.3 Clocked Storage Elements: Latches, Master-Slave Flip-                                                                                                                                                                                                                                    | 68                                           |

| 3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies                                                                                                                                                                                                         | 68<br>70                                     |

| <ul><li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies.</li><li>3.4 Timing Features of Clocked Storage Elements.</li></ul>                                                                                                                             | 68<br>70<br>75                               |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li> <li>3.4 Timing Features of Clocked Storage Elements</li> <li>3.5 Clock Uncertainties Absorption and Time Borrowing</li> </ul>                                                             | 68<br>70<br>75<br>82                         |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li> <li>3.4 Timing Features of Clocked Storage Elements</li> <li>3.5 Clock Uncertainties Absorption and Time Borrowing</li> <li>3.6 Energy Consumption in Clocked Storage Elements</li> </ul> | 68<br>70<br>75<br>82<br>85                   |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li></ul>                                                                                                                                                                                      | 70<br>75<br>82<br>85<br>86                   |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li></ul>                                                                                                                                                                                      | 70<br>75<br>82<br>85<br>86<br>88             |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li></ul>                                                                                                                                                                                      | 70<br>75<br>82<br>85<br>86                   |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li></ul>                                                                                                                                                                                      | 68<br>70<br>75<br>82<br>85<br>86<br>88       |

| <ul> <li>3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies</li></ul>                                                                                                                                                                                      | 68<br>70<br>75<br>82<br>85<br>86<br>88       |

| 3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies                                                                                                                                                                                                         | 68<br>70<br>75<br>82<br>85<br>86<br>88<br>89 |

| 3.3 Clocked Storage Elements: Latches, Master-Slave Flip-Flops and Pulsed Topologies                                                                                                                                                                                                         | 68<br>70<br>75<br>82<br>85<br>86<br>88<br>89 |

| 4.2.2 Two different re-converging paths                                                                                                 | 9/  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2.3 A bifurcating path                                                                                                                | 99  |

| 4.2.4 Other cases                                                                                                                       | 99  |

| 4.3 Sizing of Dependent Design Variables – Step 2                                                                                       | 99  |

| 4.3.1 Clocked precharge transistors                                                                                                     | 101 |

| 4.3.2 Keepers and noise immunity                                                                                                        | 102 |

| 4.3.3 Feedback paths                                                                                                                    | 103 |

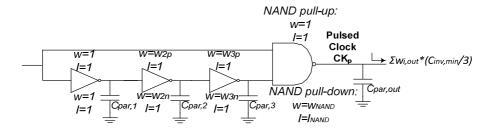

| 4.3.4 Pulse generators                                                                                                                  | 103 |

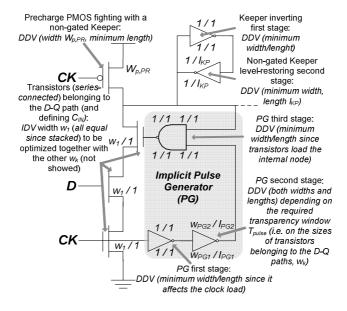

| 4.3.5 IDVs and DDVs in SDFF first stage                                                                                                 | 106 |

| 4.4 Estimation of Design Space (IDVs) Bounds – Step 3                                                                                   | 107 |

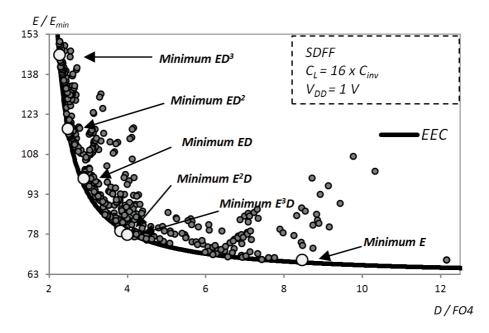

| 4.5 Extrapolation of the Energy-Efficient Curve – Step 4                                                                                | 107 |

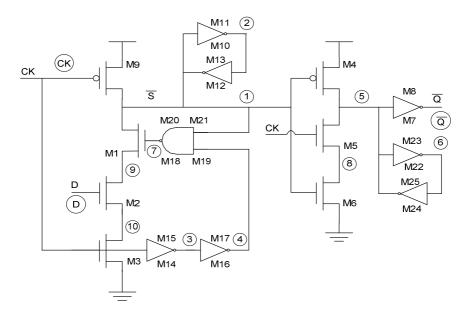

| <ul><li>4.6 A Complete Design Example: the SDFF Case of Study</li><li>4.7 Estimation of Layout Parasitics in Transistor-Level</li></ul> | 107 |

| Design Iterations                                                                                                                       | 113 |

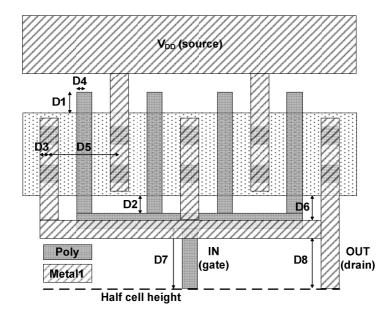

| 4.7.1 Estimation of layout parasitics from stick diagrams                                                                               | 114 |

| 4.7.2 A detailed example: geometrical width of folded transistors                                                                       | 115 |

| 4.7.3 The SDFF case of study                                                                                                            | 116 |

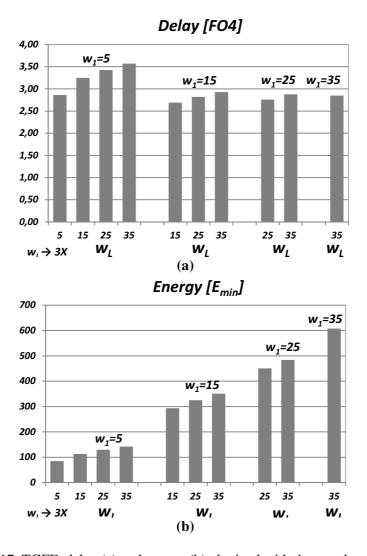

| A.4 Reconsidering High-Speed Design Criteria for Transmission-Gate Based Master-Slave Flip-Flops                                        | 118 |

| A.4.1 Timing behavior of TGMS flip-flops                                                                                                | 119 |

| A.4.2 High-speed design strategy for TGMS flip-flops                                                                                    | 120 |

| A.4.3 Design example: TGFF                                                                                                              | 123 |

| A.4.4 Simulation results                                                                                                                | 126 |

| 5. ANALYSIS AND COMPARISON IN THE                                                                                                       | 101 |

| ENERGY-DELAY-AREA DOMAIN                                                                                                                | 131 |

| 5.1 A Thorough Analysis and Comparison Strategy                                                                                         | 131 |

| 5.2 Simulation Setup and Energy-Delay Estimation                                                                                        | 133 |

| 5.2.1 Test bench circuit                                                                                                                | 133 |

| 5.2.2 Definition of timing figure of merit                                                                                              | 134 |

| 5.2.3 Estimation of energy dissipation                                                                                                  | 135 |

| 5.3 Analyzed CSE Classes and Topologies                                                                                                 | 140 |

| 5.4 Normalization to Technology                                                                                                         | 142 |

| 5.5 Energy-Delay Tradeoff in Each Class                                                                                                 | 147 |

XII Table of Contents

|   | 5.5.1 Single Edge-Triggered Master-Slave CSEs                               | 147 |

|---|-----------------------------------------------------------------------------|-----|

|   | 5.5.2 Single Edge-Triggered Implicitly-Explicitly Pulsed CSEs               | 149 |

|   | 5.5.3 Single Edge-Triggered Differential CSEs                               | 153 |

|   | 5.5.4 Dual Edge-Triggered CSEs                                              | 155 |

|   | 5.6 Energy-Delay Global Comparison Among All CSEs                           | 159 |

|   | $5.6.1  E^i D^j$ metrics                                                    | 159 |

|   | 5.6.2 Selection of the most energy-efficient CSEs                           | 161 |

|   | 5.7 Leakage                                                                 | 164 |

|   | 5.7.1 Leakage impact in active mode                                         | 164 |

|   | 5.7.2 Leakage impact in standby mode and tradeoff with delay                | 166 |

|   | 5.7.3 Effectiveness of leakage reduction techniques                         | 168 |

|   | 5.8 Silicon Area                                                            | 169 |

|   | 5.8.1 Comparison of CSEs area                                               | 169 |

|   | 5.8.2 Area-delay tradeoff                                                   | 171 |

|   | 5.8.3 Area related properties                                               | 172 |

|   | 5.9 Clock Load                                                              | 173 |

|   | 5.9.1 Clock load comparison and tradeoff with delay                         | 173 |

|   | 5.9.2 Impact of layout parasitics on the clock load                         | 175 |

|   | 5.9.3 Joint CSEs and clock distribution energy dissipation                  | 175 |

|   | 5.10 Summary                                                                | 178 |

|   |                                                                             |     |

| 6 | . ENERGY-EFFICIENT CLOCK SLOPE                                              |     |

| L | DESIGN AT THE CLOCK DOMAIN LEVEL                                            | 181 |

|   | 6.1 Basic Consideration on the Role of the Clock Slope                      | 181 |

|   | 6.2 Setup to Simulate CSEs Under a Varying Clock Slope                      | 182 |

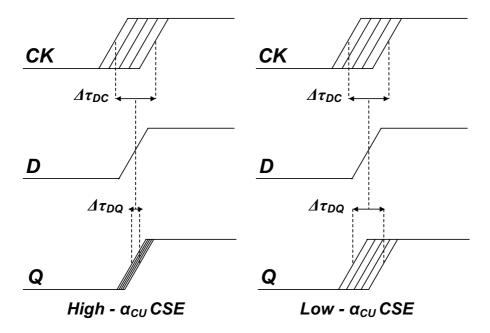

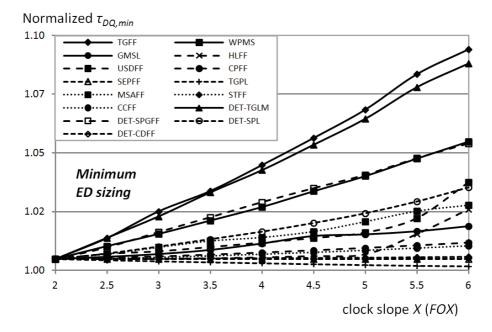

|   | 6.3 CSEs Timing and Energy Versus Clock Slope                               | 184 |

|   | 6.3.1 Impact of clock slope on $\tau_{DQ,min}$                              | 184 |

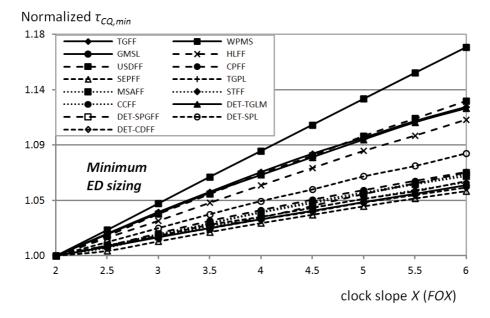

|   | 6.3.2 Impact of clock slope on $\tau_{CQ,min}$ , $t_{setup}$ and $t_{hold}$ | 185 |

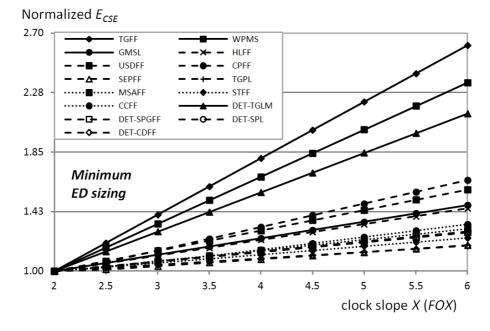

|   | 6.3.3 Impact of clock slope on $E_{CSE}$ and operation robustness           | 187 |

|   | 6.4 Energy of Local Clock Buffers Versus Clock Slope                        | 188 |

|   | 6.5 Design Considerations and Optimum Clock Slope                           | 192 |

|   | 6.5.1 Analytical evaluation of the optimum clock slope                      | 192 |

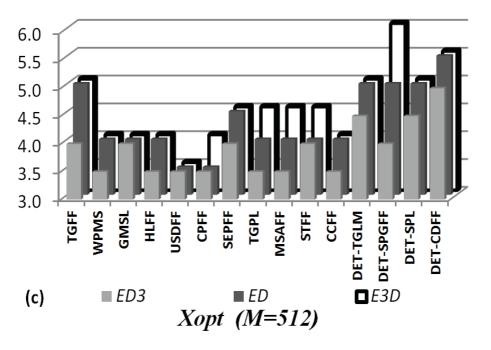

|   | 6.5.2 Dependencies and typical optimum clock slope $X_{opt}$                | 193 |

|   | 6.5.3 Effectiveness of clock slope optimization and CSEs comparison         | 196 |

|   |                                                                             |     |

Table of Contents XIII

| 6.6 Impact of Clock Slope on Skew, Jitter and Variability           | 201 |

|---------------------------------------------------------------------|-----|

| 6.6.1 Additive skew and jitter due to a smoother clock slope        | 201 |

| 6.6.2 The impact of clock slope on CSEs delay variability           | 204 |

| 6.7 The Impact of Technology Scaling                                | 206 |

| 7. NOVEL ULTRA-FAST AND ENERGY-                                     |     |

| EFFICIENT PULSED LATCH TOPOLOGIES                                   | 209 |

| 7.1 State of the Art and Preliminary Considerations                 | 209 |

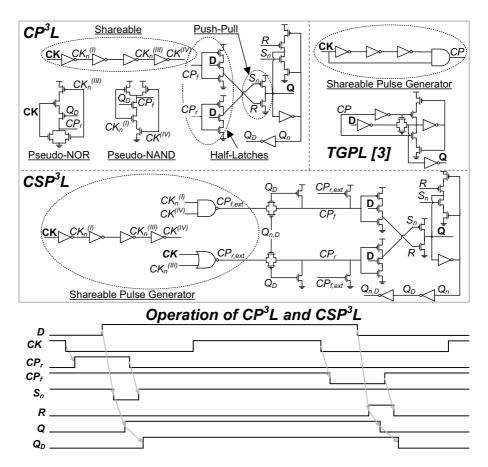

| 7.2 Operation of the Novel CP <sup>3</sup> L and CSP <sup>3</sup> L | 210 |

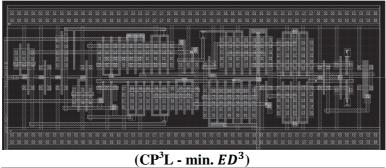

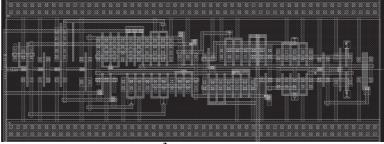

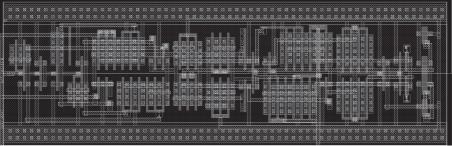

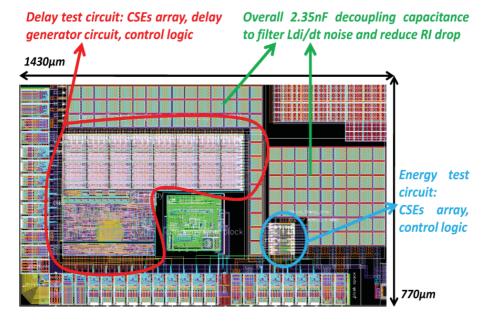

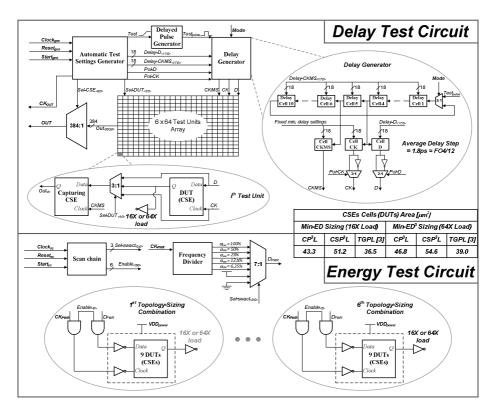

| 7.3 Test Chip and Circuits for Delay-Energy Measurement             | 213 |

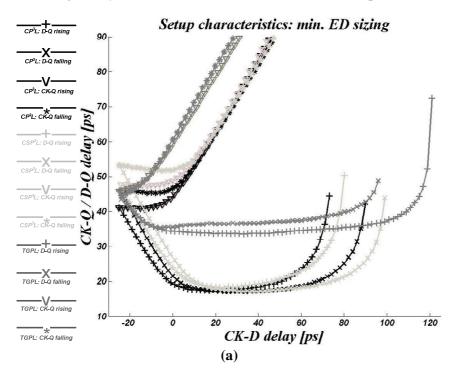

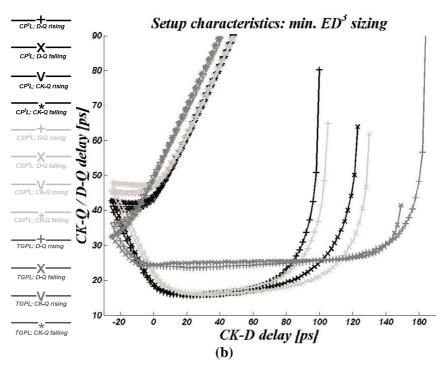

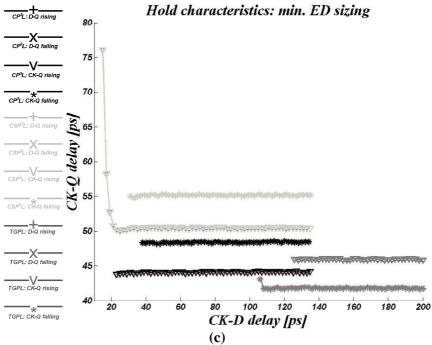

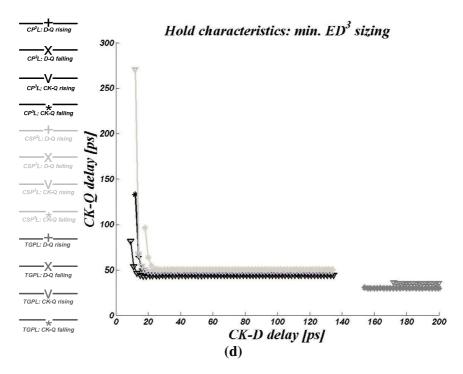

| 7.4 Setup and Hold Timing Characteristics                           | 218 |

| 7.5 Dissipation and Energy/Leakage-Delay Tradeoffs                  | 222 |

| 7.6 Variability of Timing Parameters and Leakage                    | 224 |

| 7.7 Performances Summary and Comparison                             | 225 |

| CONCLUSION                                                          | 227 |

| REFERENCES                                                          | 231 |

List of Figures XV

# LIST OF FIGURES

| CMOS logic gates seen as decoupled RC blocks                                                                                 | 6                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Geometrical interpretation of logical effort and parasitic delay                                                             | 10                                                                                                                                          |

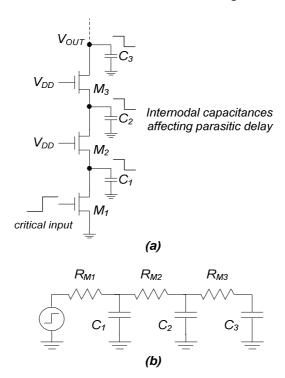

| Application of the Elmore delay theory to deal with stacked                                                                  |                                                                                                                                             |

| transistors and internodal capacitances (a) through an equivalent                                                            |                                                                                                                                             |

| <i>RC</i> tree (b)                                                                                                           | 12                                                                                                                                          |

| Sizing of basic gates under unitary skew conditions                                                                          | 14                                                                                                                                          |

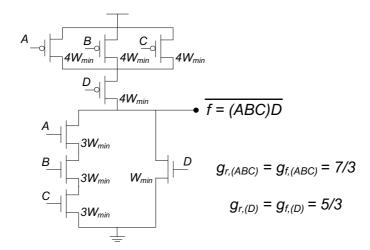

| Complex gate sized to exhibit $S = 1$ skew and delay equal to a minimum inverter: differences in $g$ values according to the |                                                                                                                                             |

| considered input                                                                                                             | 16                                                                                                                                          |

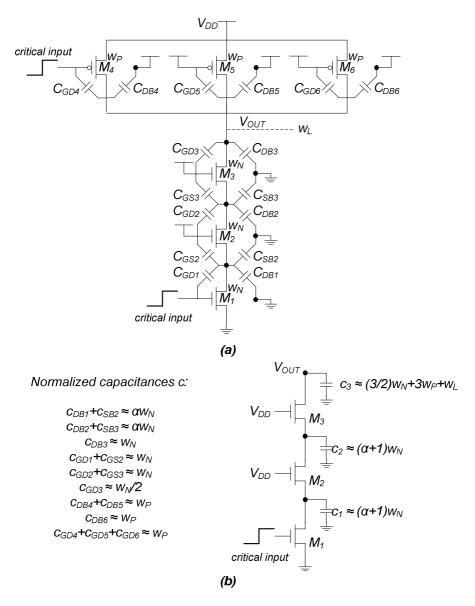

| Internodal capacitances in a NAND3 (a) and accurate                                                                          |                                                                                                                                             |

| estimation of their normalized values as functions of sizing (b)                                                             | 18                                                                                                                                          |

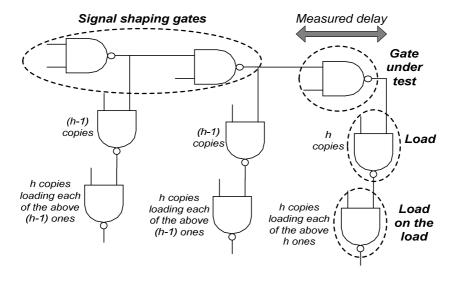

| Simulations testbench to extract $g$ and $p$ ( $h$ is the electrical                                                         |                                                                                                                                             |

| effort)                                                                                                                      | 20                                                                                                                                          |

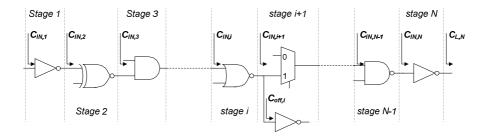

| Multistage path                                                                                                              | 22                                                                                                                                          |

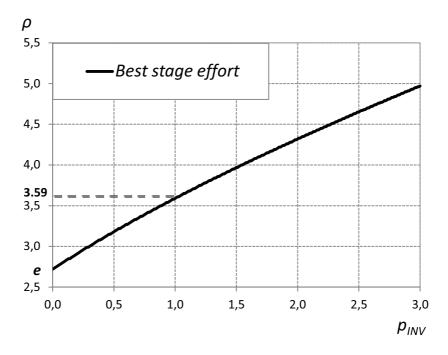

| Best stage effort vs. inverter parasitic delay                                                                               | 26                                                                                                                                          |

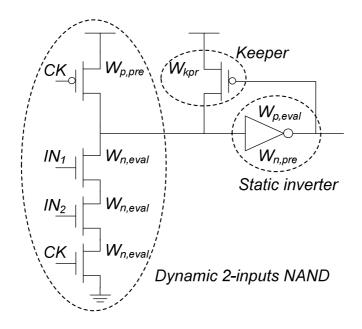

| Domino gate compound of a typically low-skewed dynamic NAND2, a typically high-skewed static inverter and a PMOS             |                                                                                                                                             |

|                                                                                                                              | 27                                                                                                                                          |

| 1                                                                                                                            |                                                                                                                                             |

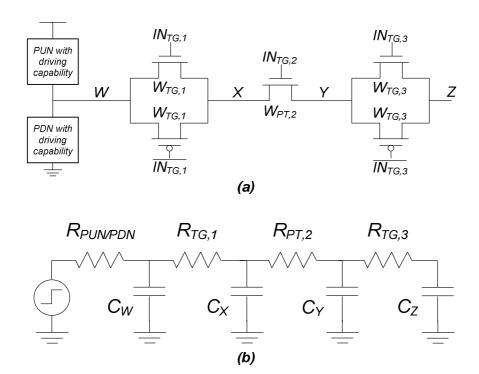

| reduction to an equivalent RC tree (b)                                                                                       | 29                                                                                                                                          |

| Capacitive contributions determining dynamic energy in a gate                                                                | 34                                                                                                                                          |

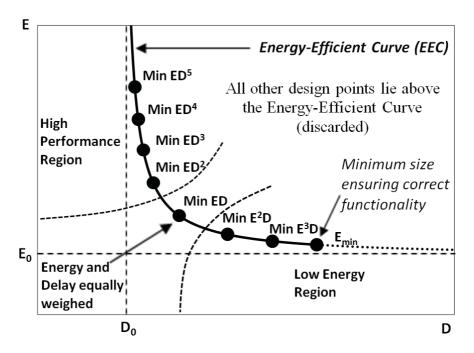

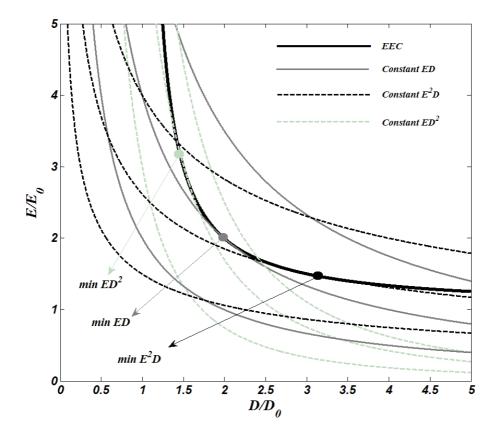

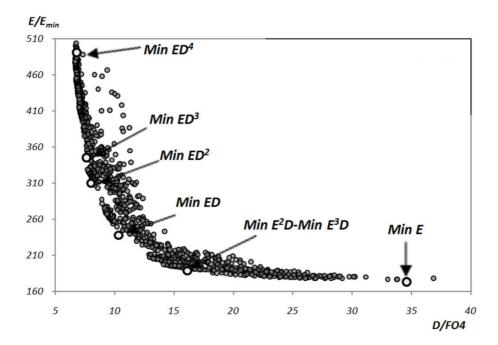

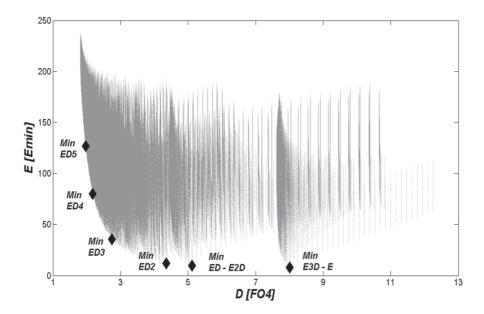

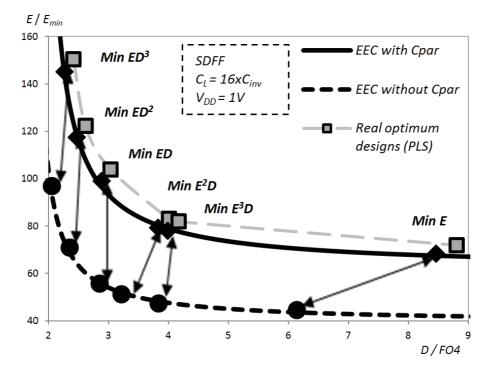

| Energy-efficient curve and designs optimizing the metrics $E^iD^j$                                                           | 39                                                                                                                                          |

| Typical energy-efficient curve and constant cost function                                                                    |                                                                                                                                             |

| contours for $j/i = 1.0$ , $j/i = 0.5$ and $j/i = 2.0$                                                                       | 42                                                                                                                                          |

|                                                                                                                              | Application of the Elmore delay theory to deal with stacked transistors and internodal capacitances (a) through an equivalent $RC$ tree (b) |

XVI List of Figures

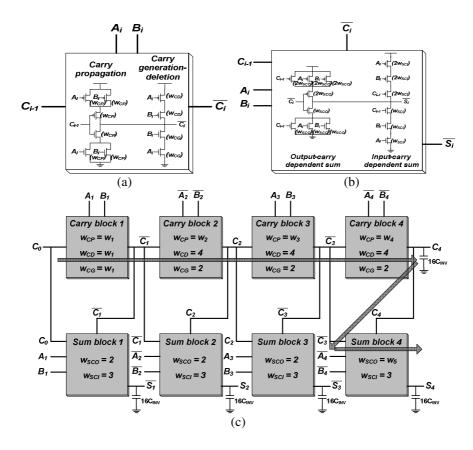

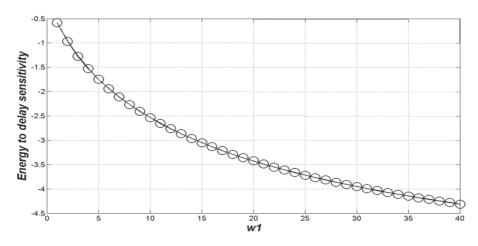

| 2.4<br>2.5 | 4-bit RCA: carry block (a), sum block (b), whole structure (c) 4-bit RCA: energy-to-delay sensitivity of Logical Effort designs | 50  |

|------------|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.5        | as a function of the first stage size                                                                                           | 50  |

| 2.6        | $E-D$ space exploration for the 4-bit RCA ( $C_L=16C_{IN}$ ),                                                                   | 50  |

| 2.0        | $V_{DD} = 1V$ )                                                                                                                 | 52  |

| 2.7        | Full $E - D$ space exploration for a buffered 2:1 multiplexer                                                                   | 53  |

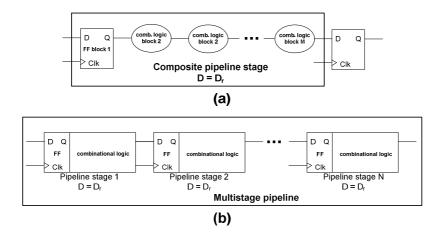

| 2.8        | Composite pipeline stage (a) and multistage pipeline (b)                                                                        | 56  |

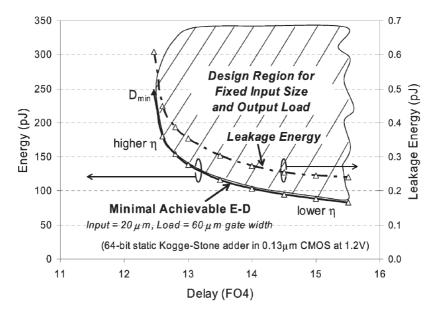

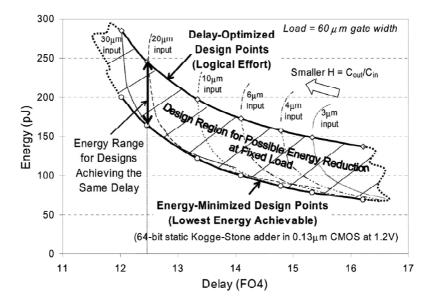

| 2.9        | 64-bit Kogge-Stone adder: energy-delay optimization under                                                                       |     |

| ,          | fixed input capacitance and output load [DZ006]                                                                                 | 61  |

| 2.10       | 64-bit Kogge-Stone adder: design region for possible energy-                                                                    | 0.1 |

|            | delay reduction under varying input capacitance and fixed                                                                       |     |

|            | output load [DZO06]                                                                                                             | 61  |

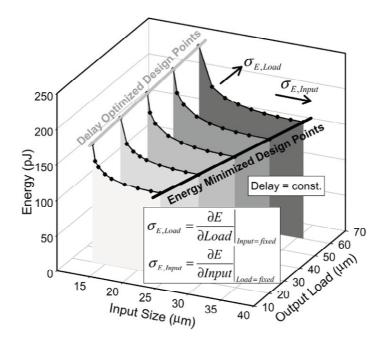

| 2.11       | Optimized energy of a pipeline stage versus input capacitance                                                                   | -   |

|            | under fixed load and versus load under fixed input capacitance                                                                  |     |

|            | [DZO06]                                                                                                                         | 62  |

|            | [                                                                                                                               | -   |

| 3.1        | Finite state machine                                                                                                            | 66  |

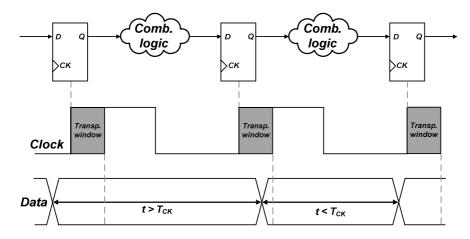

| 3.2        | Pipelining                                                                                                                      | 67  |

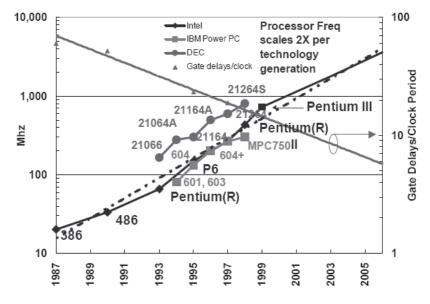

| 3.3        | Clock frequencies and logic depths in microprocessors [O02]                                                                     | 67  |

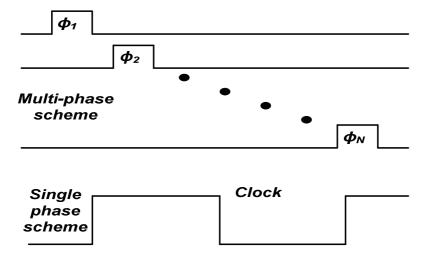

| 3.4        | Multi-phases and single-phase clocking schemes                                                                                  | 68  |

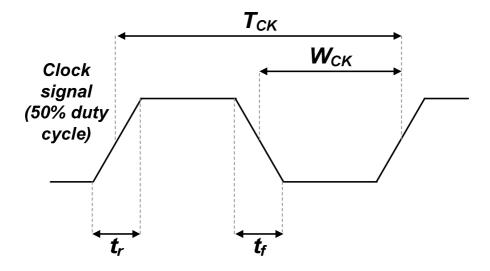

| 3.5        | The clock signal and its parameters                                                                                             | 69  |

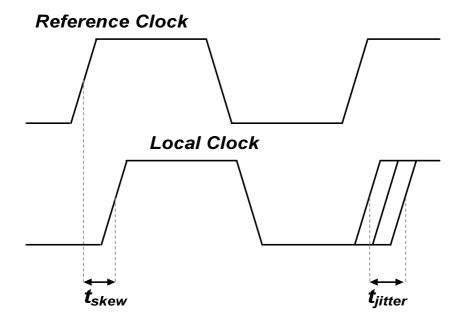

| 3.6        | Clock skew and clock jitter                                                                                                     | 70  |

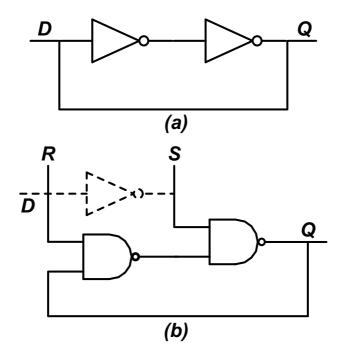

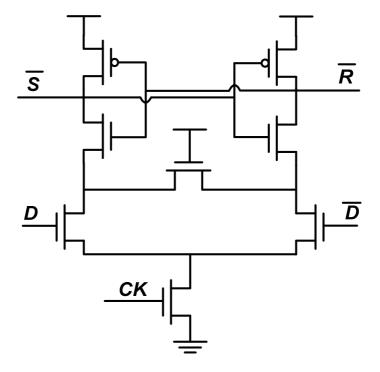

| 3.7        | Keeper and Set-Reset memory element                                                                                             | 71  |

| 3.8        | Clocked D latch                                                                                                                 | 72  |

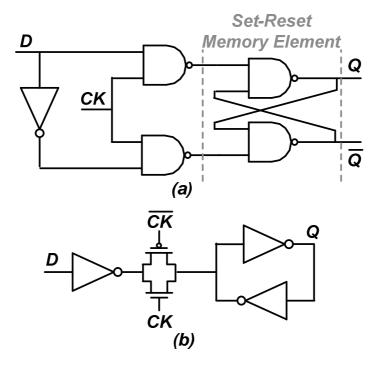

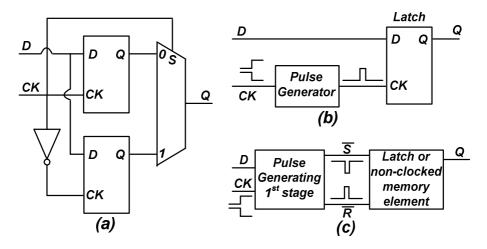

| 3.9        | Master-Slave CSEs (FFs)                                                                                                         | 73  |

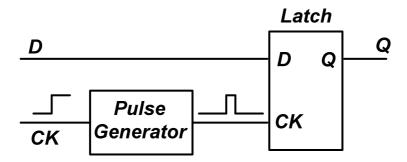

| 3.10       | Explicitly Pulsed CSEs (Pulsed Latches)                                                                                         | 74  |

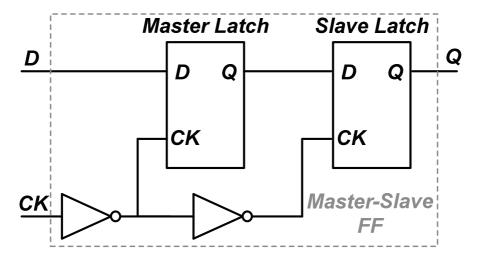

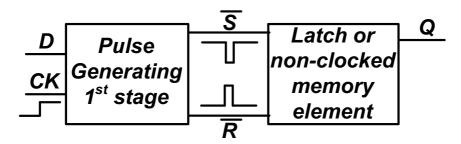

| 3.11       | Implicitly Pulsed CSEs                                                                                                          | 75  |

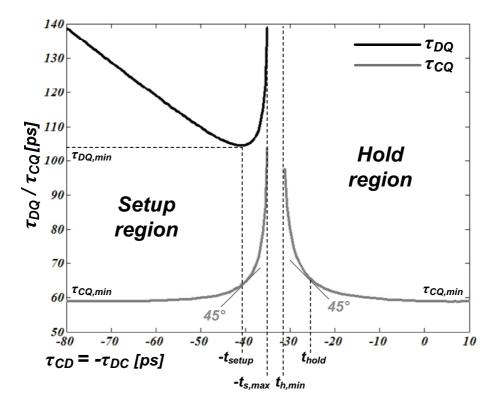

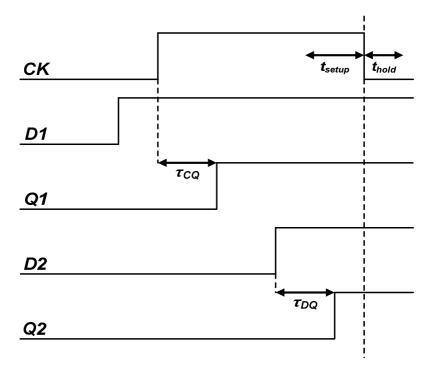

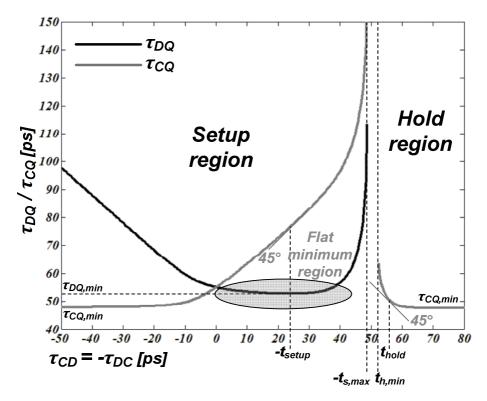

| 3.12       | $\tau_{CQ} / \tau_{DQ}$ vs. $\tau_{CD} = -\tau_{DC}$ timing curves in a Master-Slave FF                                         | 76  |

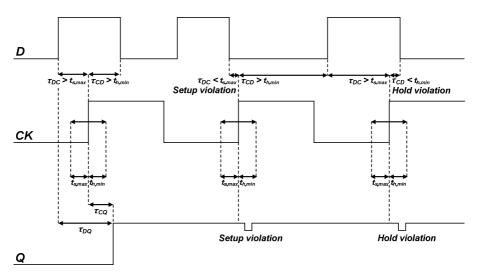

| 3.13       | Timing diagram and setup/hold times violations in a positive                                                                    |     |

|            | edge-triggered CSE                                                                                                              | 77  |

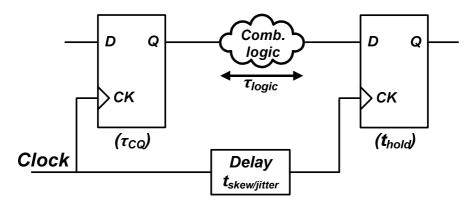

| 3.14       | Pipeline stages in a datapath                                                                                                   | 79  |

| 3.15       | Timing diagrams of a latch transparent during high clock phase.                                                                 | 81  |

| 3.16       | $\tau_{CQ} / \tau_{DQ}$ vs. $\tau_{CD} = -\tau_{DC}$ timing curves in a Pulsed CSE                                              | 82  |

| 3.17       | Clock uncertainties absorption.                                                                                                 | 84  |

| 3.18       | Time borrowing                                                                                                                  |     |

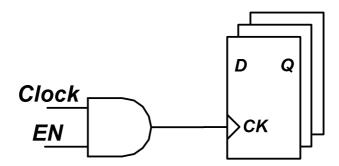

| 3.19       | Clock gating                                                                                                                    | 87  |

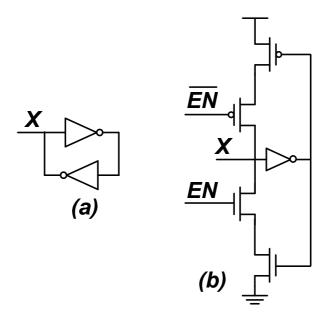

| 3.20       | Non-gated (a) and gated (b) keepers                                                                                             | 89  |

| 3.21       | Sense-amplifying input stage in a differential CSE                                                                              | 90  |

| 3.22       | Master-Slave (a), Explicitly Pulsed (b) and Implicitly Pulsed (c)                                                               |     |

|            | Dual Edge-Triggered CSEs                                                                                                        | 91  |

| 4.1        | Summary of the proposed design procedure                                                                                        | 95  |

| 4.2        | D - Q paths in the TGFF circuit (a single path)                                                                                 | 98  |

List of Figures XVII

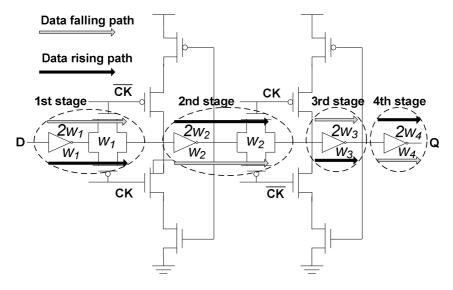

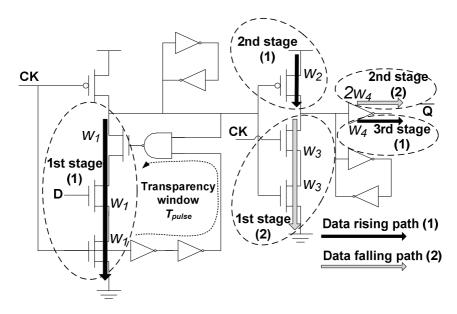

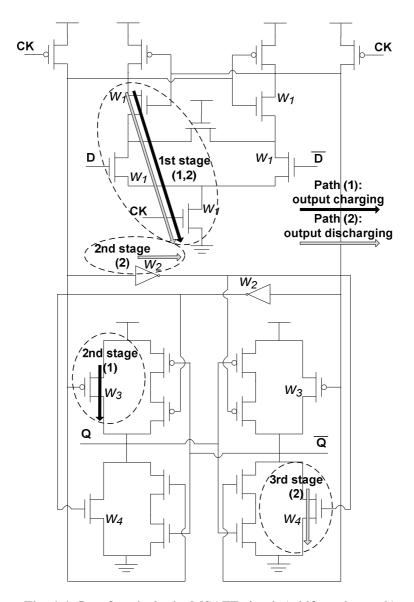

| 4.3  | D-Q paths in the SDFF circuit (two re-converging paths)                                                                  | 98   |

|------|--------------------------------------------------------------------------------------------------------------------------|------|

| 4.4  | D - Q paths in the MSAFF circuit (a bifurcating path)                                                                    | 100  |

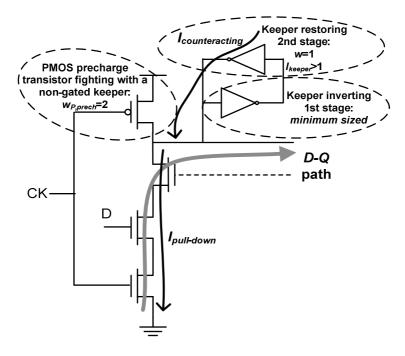

| 4.5  | Counteractive action due to non-gated keeper                                                                             | 103  |

| 4.6  | Typical implementation of a pulse generator                                                                              | 104  |

| 4.7  | SDFF: exemplification of IDVs and DDVs                                                                                   | 106  |

| 4.8  | SDFF schematic                                                                                                           | 108  |

| 4.9  | E - D space exploration for the SDFF                                                                                     | 112  |

| 4.10 | EECs of SDFF with and without interconnect parasitic                                                                     | 113  |

| 4.11 | PMOS with source at $V_{DD}$ and local gate- and drain- wires                                                            | 115  |

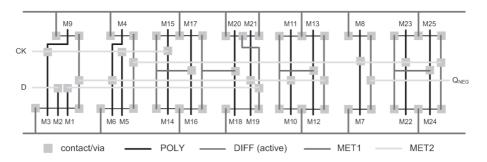

| 4.12 | Stick diagram of the SDFF                                                                                                | 117  |

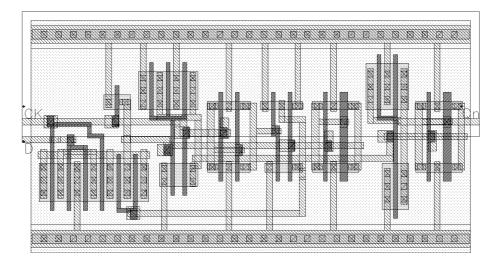

| 4.13 | Layout of the SDFF (min. ED product sizing)                                                                              | 117  |

| 4.14 | Structure of a generic TG (or PT) –based FF                                                                              | 120  |

| 4.15 | Gates at the boundary between Master and Slave latches                                                                   | 121  |

| 4.16 | Schematic of the TGFF (a) and LE parameters according to the                                                             |      |

|      | traditional and proposed approaches                                                                                      | 124  |

| 4.17 | TGFF: delay (a) and energy (b) obtained with the novel                                                                   | 4.00 |

| 4.10 | approach                                                                                                                 | 128  |

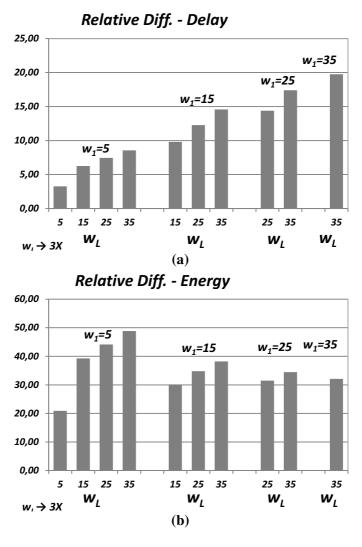

| 4.18 | TGFF: Relative percentage delay (a) and energy (b) differences                                                           | 120  |

|      | between the traditional and proposed approaches                                                                          | 129  |

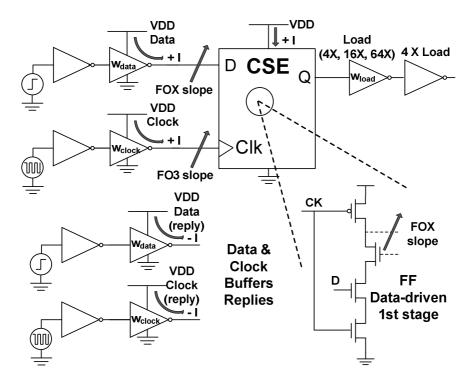

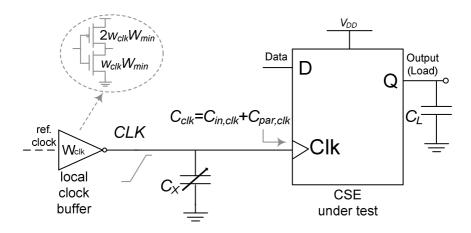

| 5.1  | Test hands circuit used to abarectorize a conoria CSE                                                                    | 134  |

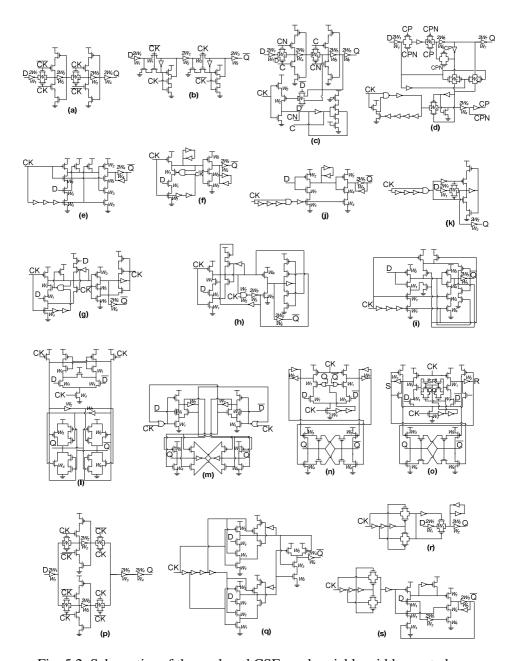

| 5.2  | Test bench circuit used to characterize a generic CSE<br>Schematics of the analyzed CSEs and variable widths $w_k$ to be | 134  |

| 3.4  | optimized: TGFF (a), WPMS (b), GMSL (c), DTLA (d), HLFF                                                                  |      |

|      | (e), SDFF (f), USDFF (g), IPPFF (h), CPFF (i), SEPFF (j),                                                                |      |

|      | TGPL (k), MSAFF (l), STFF (m), CCFF (n), VSWFF (o), DET-                                                                 |      |

|      | TGLM (p), DET-SPGFF (q), DET-SPL (r), DET-CDFF (s)                                                                       | 141  |

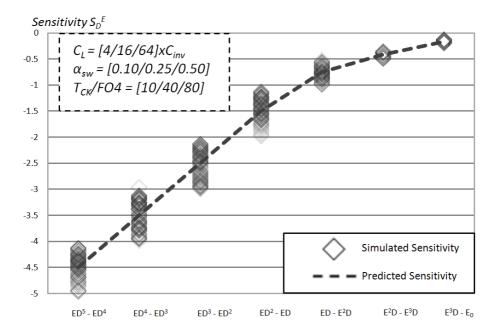

| 5.3  | Sensitivity analyses for the optimum designs                                                                             | 143  |

| 5.4  | Layouts of the analyzed CSEs (min. ED sizing)                                                                            | 147  |

| 5.5  | EECs of MS CSEs: $C_L = 16C_{inv,min}$ , $\alpha_{sw} = 0.25$ , $T_{CK}/F04 =$                                           |      |

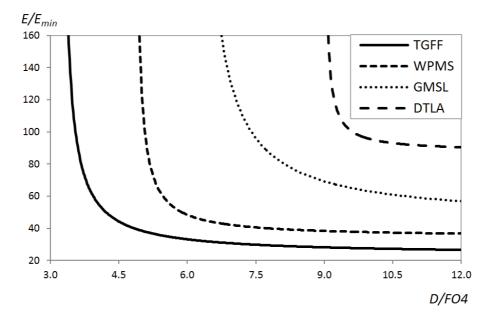

|      | 40                                                                                                                       | 148  |

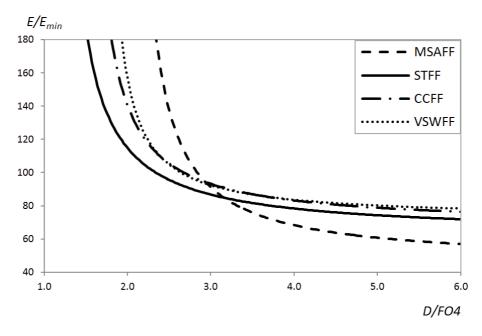

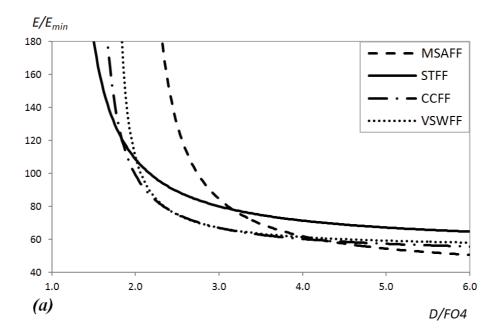

| 5.6  | EECs of IP-EP CSEs: $C_L = 16C_{inv,min}$ , $\alpha_{sw} = 0.25$ ,                                                       |      |

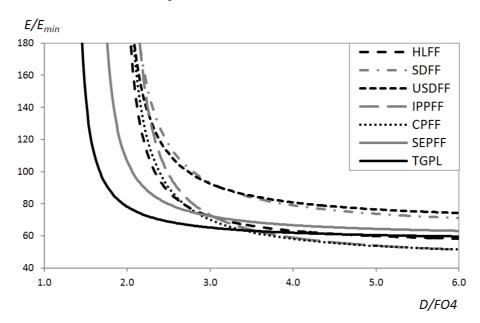

|      | $T_{CK}/F04 = 40$                                                                                                        | 149  |

| 5.7  | EECs of IP-EP CSEs: $C_L = 64C_{inv,min}$ (a) and $C_L = 4C_{inv,min}$                                                   |      |

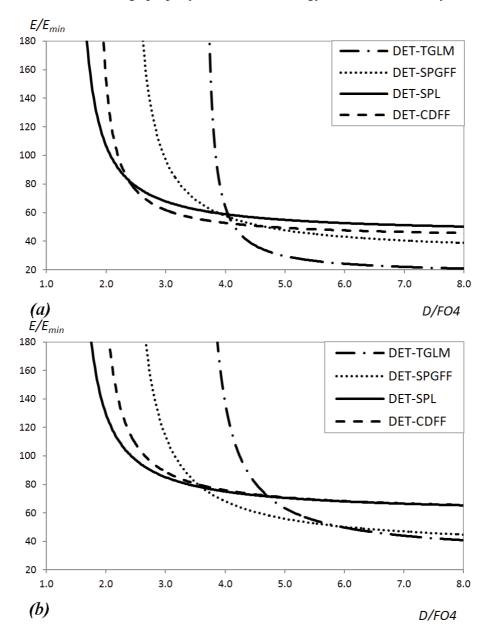

|      | (b) $(\alpha_{SW} = 0.25, T_{CK}/F04 = 40)$                                                                              | 151  |

| 5.8  | EECs of IP-EP CSEs: $\alpha_{sw} = 0.1$ (a) and $\alpha_{sw} = 0.5$ (b)                                                  | 101  |

| J.0  | $(C_L = 16C_{inv,min}, T_{CK}/F04 = 40)$                                                                                 | 152  |

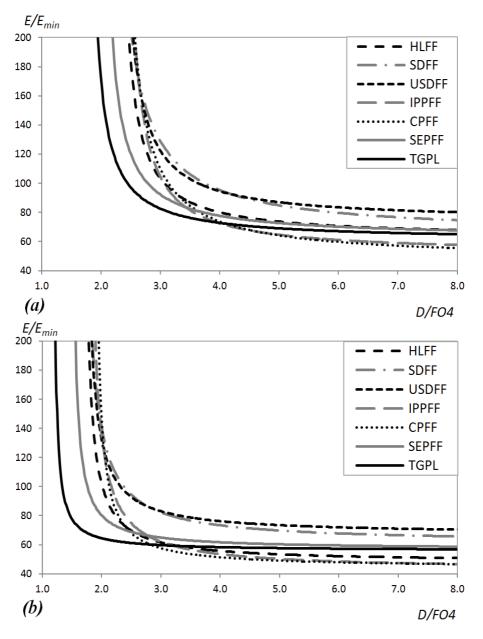

| 5.9  | EECs of Differential CSEs: $C_L = 16C_{inv,min}$ , $\alpha_{sw} = 0.25$ ,                                                | 132  |

| J.)  | $T_{CK}/F04 = 40$                                                                                                        | 153  |

| 5.10 | EECs of Differential CSEs: $\alpha_{sw} = 0.1$ (a) and $\alpha_{sw} = 0.5$ (b)                                           | 133  |

| J.10 | $(C_L = 16C_{inv,min}, T_{CK}/F04 = 40)$                                                                                 | 155  |

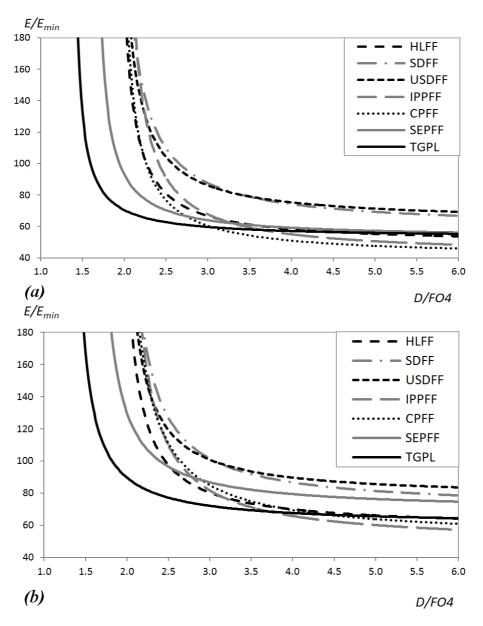

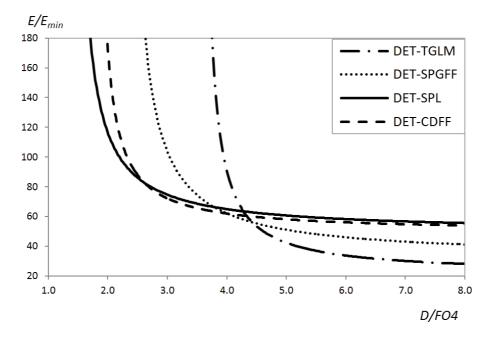

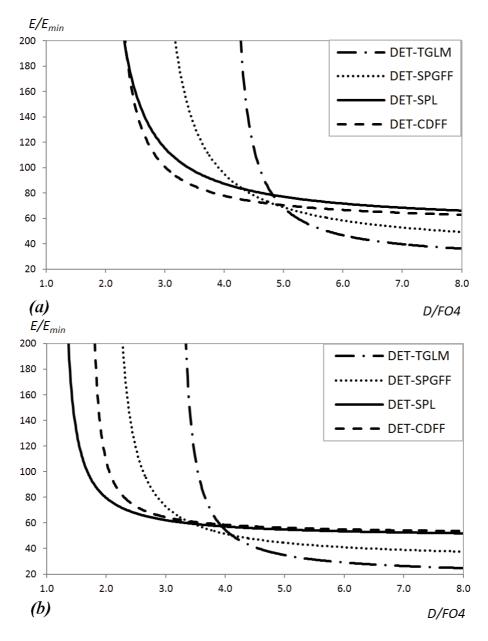

| 5.11 | EECs of DET CSEs: $C_L = 16C_{inv,min}$ , $\alpha_{sw} = 0.25$ ,                                                         | 133  |

| J.11 |                                                                                                                          | 156  |

|      | $T_{CK}/FO4 = 40$                                                                                                        | 130  |

XVIII List of Figures

| 5.12 | EECs of DE1 CSEs: $C_L = 64C_{inv,min}$ (a) and $C_L = 4C_{inv,min}$                |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | (b) $(\alpha_{sw} = 0.25, T_{CK}/F04 = 40)$                                         | 157 |

| 5.13 | EECs of DET CSEs: $\alpha_{sw} = 0.1$ (a) and $\alpha_{sw} = 0.5$ (b) ( $C_L =$     |     |

|      | $16C_{inv,min}, T_{CK}/F04 = 40)$                                                   | 158 |

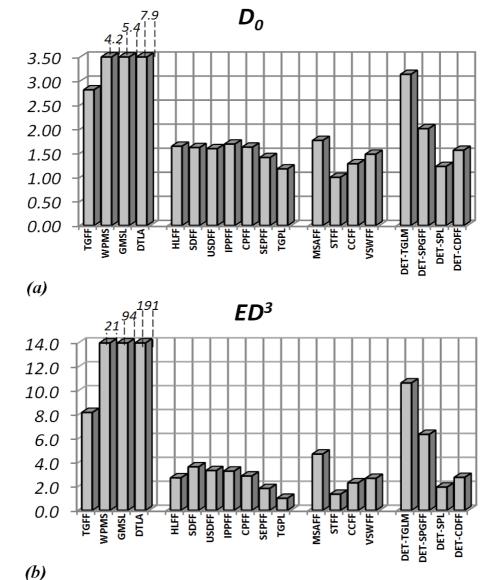

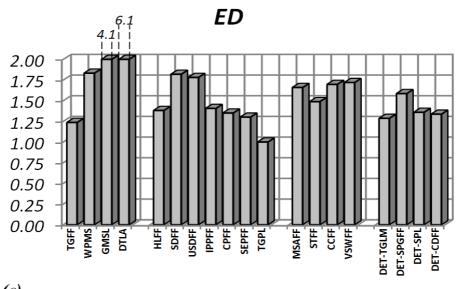

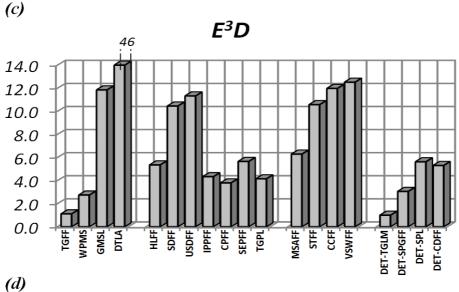

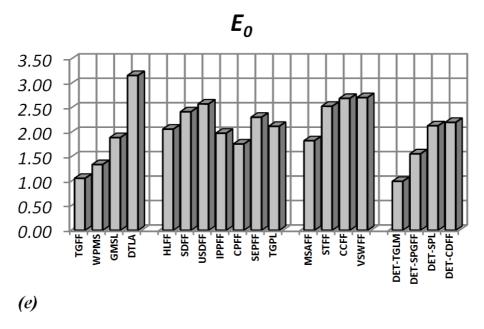

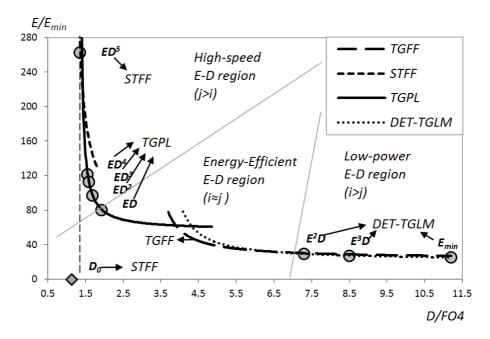

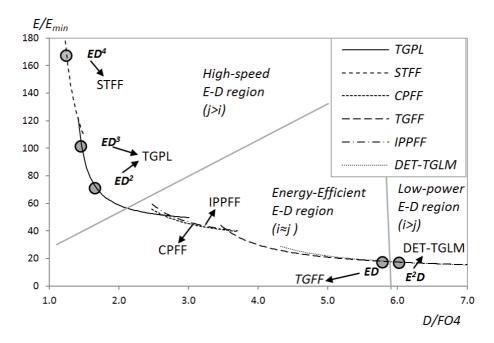

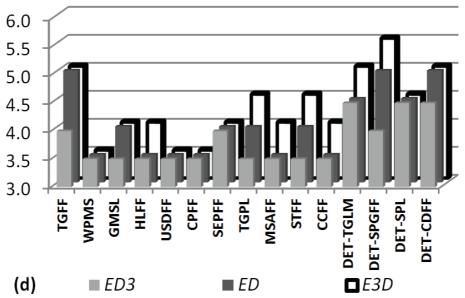

| 5.14 | $D_0$ (a), $ED^3$ (b), $ED$ (c), $E^3D$ (d), $E_0$ (e) normalized FOMs:             |     |

|      | $C_L = 16C_{inv,min}, \alpha_{sw} = 0.25, T_{CK}/F04 = 40$                          | 162 |

| 5.15 | Ideal EEC extracted selecting the most energy-efficient CSEs                        |     |

|      | and minimum- $E^iD^j$ designs                                                       | 163 |

| 5.16 | Ideal EEC extracted selecting the most energy-efficient CSEs                        |     |

|      | and minimum- $E^iD^j$ designs (layout parasitics not included)                      | 164 |

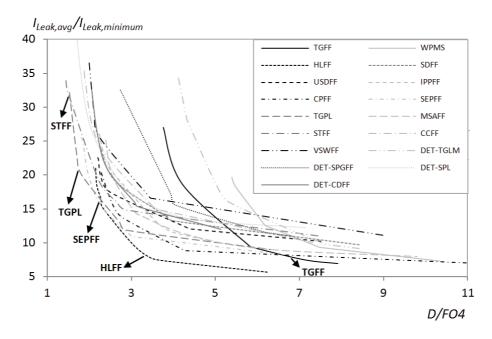

| 5.17 | Leakage-delay tradeoff. Optimization in active mode:                                |     |

|      | $C_L = 16C_{inv,min}, \alpha_{sw} = 0.25, T_{CK}/F04 = 40$                          | 167 |

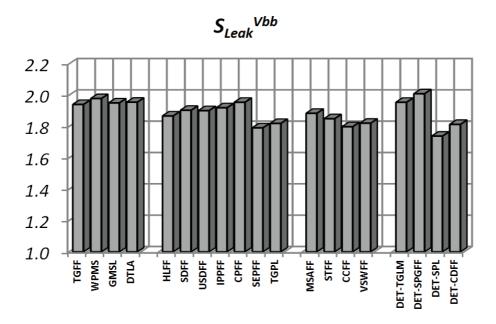

| 5.18 | Average RBB slope                                                                   | 169 |

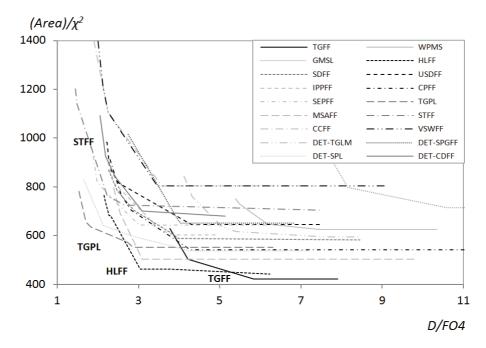

| 5.19 | Area-delay tradeoff. Optimization in active mode:                                   |     |

|      | $C_L = 16C_{inv,min}, \alpha_{sw} = 0.25, T_{CK}/F04 = 40$                          | 171 |

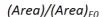

| 5.20 | Area degradation (normalization to $E_0$ sizing). Optimization in                   |     |

|      | active mode: $C_L = 16C_{inv,min}$ , $\alpha_{sw} = 0.25$ , $T_{CK}/F04 = 40$       | 172 |

| 5.21 | Clock load degradation (normalization to $E_0$ sizing).                             |     |

|      | Optimization in active mode: $C_L = 16C_{inv,min}$ , $\alpha_{sw} = 0.25$ ,         |     |

|      | $T_{CK}/FO4 = 40$                                                                   | 176 |

| 6.1  | Setup used to simulate CSEs under various clock slope values                        | 183 |

| 6.2  | Normalized (to $FO2$ case) $\tau_{DQ,min}$ vs. clock slope                          | 185 |

| 6.3  | Normalized (to $FO2$ case) $\tau_{CO,min}$ vs. clock slope                          | 187 |

| 6.4  | ζ,                                                                                  | 188 |

| 6.5  | Normalized (to $FO2$ case) $E_{CSE}$ vs. clock slope                                | 100 |

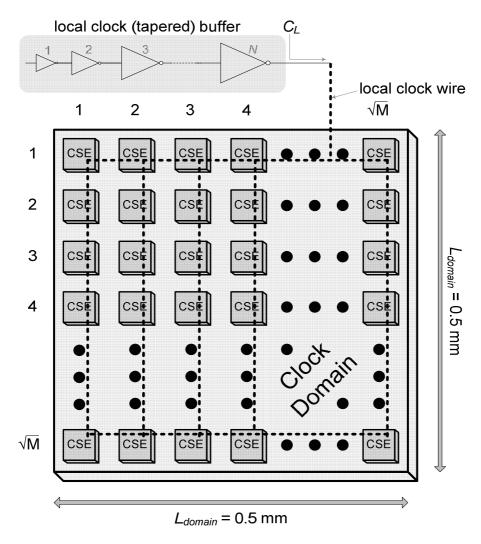

| 0.5  | domain                                                                              | 190 |

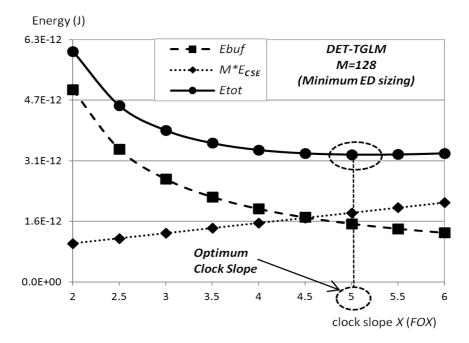

| 6.6  | $ME_{CSE}$ , $E_{buf}$ and $E_{TOT}$ vs. clock slope (DET-TGLM, $M =$               | 170 |

| 0.0  | 128)                                                                                | 194 |

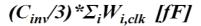

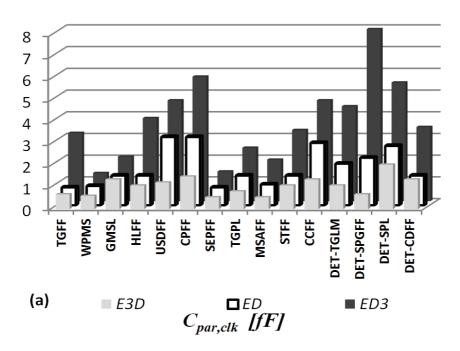

| 6.7  | Gate, $(C_{inv}/3) \sum_i w_{i,clk}$ (a), and local interconnections, $C_{par,clk}$ | 177 |

| 0.7  | (b), clock capacitances for the analyzed CSEs                                       | 195 |

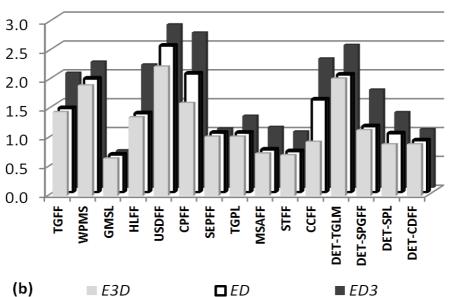

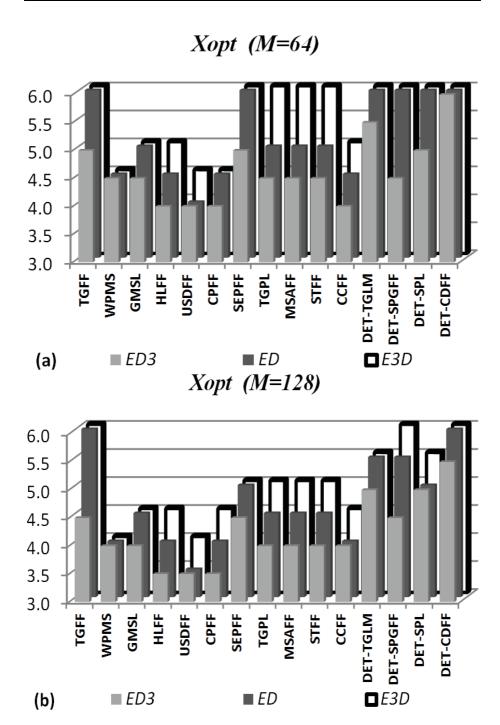

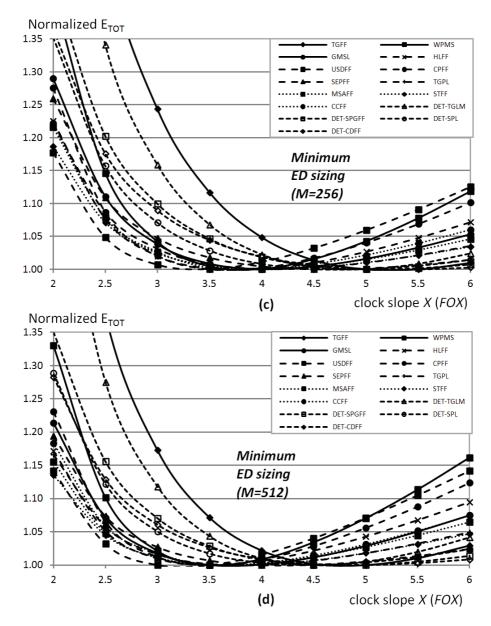

| 6.8  | Optimum clock slope $X_{opt}$ under various $M$ -values (64, 128,                   | 175 |

| 0.0  | 256 and 512) (a-d) and sizings (minimum $ED^3$ , $ED$ and $E^3D$ )                  | 198 |

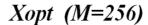

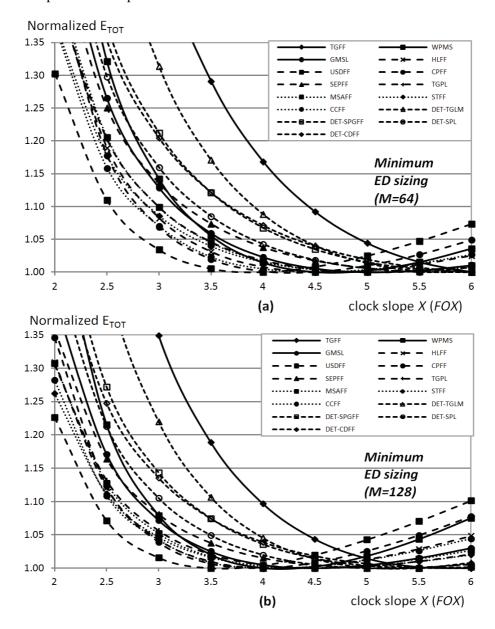

| 6.9  | Normalized $E_{TOT}$ for all CSEs with $M = 64$ (a), $M = 128$ (b),                 | 170 |

| 0.7  | M = 256  (c), M = 512  (d)                                                          | 200 |

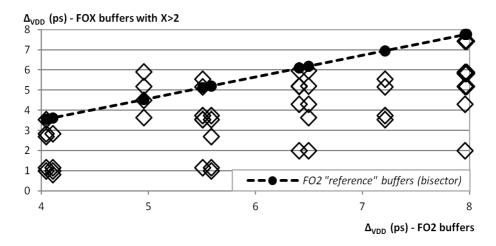

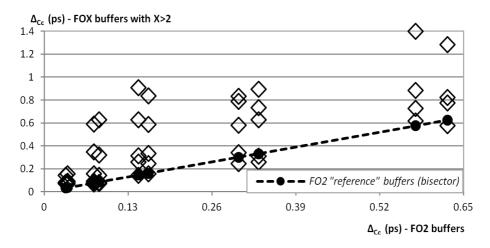

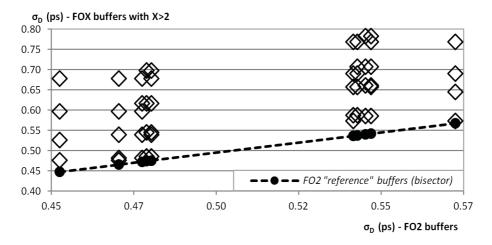

| 6.10 | $\Delta_{V_{DD}}$ of the reference buffers (with $X=2$ ) and of the buffers         | 200 |

| 0.10 | with $X > 2$ driving the same load                                                  | 203 |

| 6.11 | $\Delta_{C_C}$ of the reference buffers (with $X=2$ ) and of the buffers            | 203 |

| 0.11 | C                                                                                   | 203 |

|      | with $Y > 2$ driving the same load                                                  |     |

| 6.12 | with $X > 2$ driving the same load                                                  | 203 |

| 6.12 | with $X > 2$ driving the same load                                                  | 203 |

List of Figures XIX

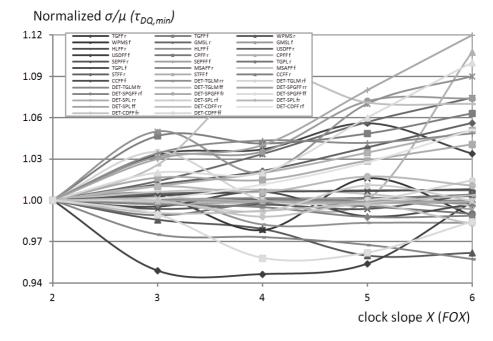

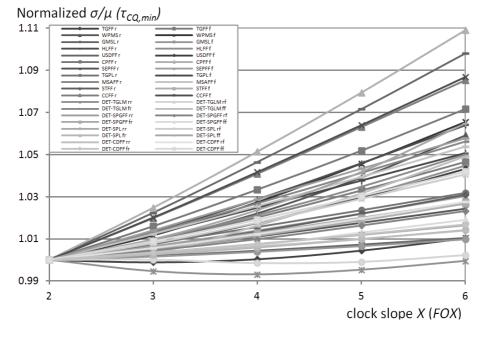

| 6.13 | Normalized $(\sigma/\mu)_{\tau_{DQ,min}}$ vs. clock slope                  | 205 |

|------|----------------------------------------------------------------------------|-----|

| 6.14 | Normalized $(\sigma/\mu)_{\tau_{CQ,min}}$ vs. clock slope                  |     |

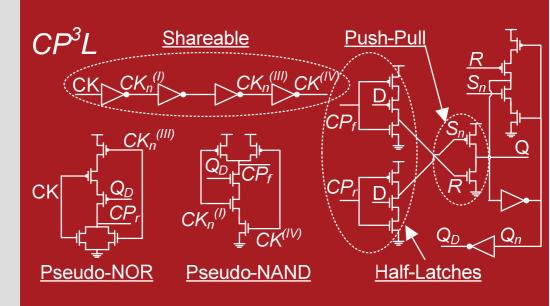

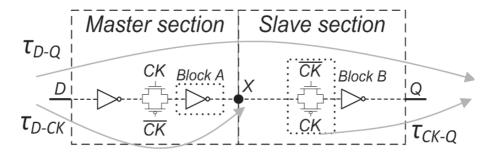

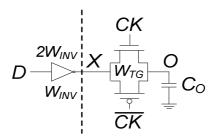

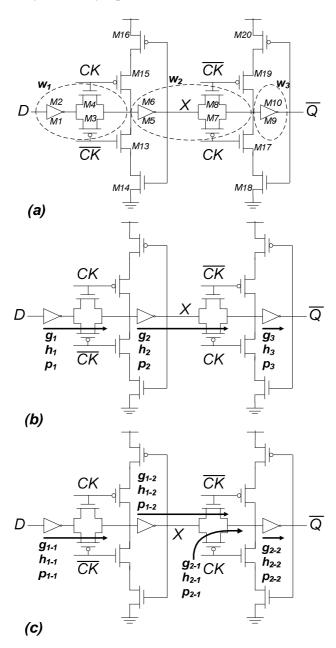

| 7.1  | Schematics and operation of CP <sup>3</sup> L, CSP <sup>3</sup> L and TGPL | 211 |

| 7.2  | Layouts of the integrated CSEs (min. $ED^3$ and $ED$ sizings)              | 213 |

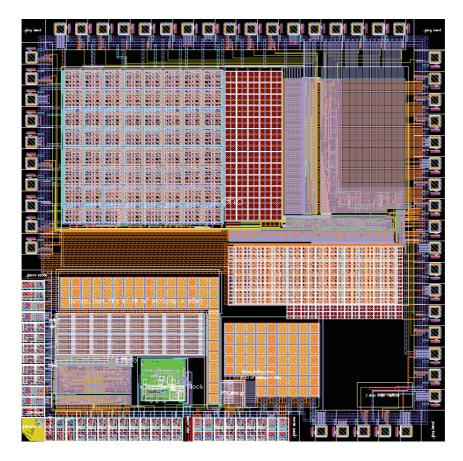

| 7.3  | Micrograph of the chip in 65-nm STCMOS065 technology                       | 214 |

| 7.4  | Layout of the chip in 65-nm STCMOS065 technology                           | 215 |

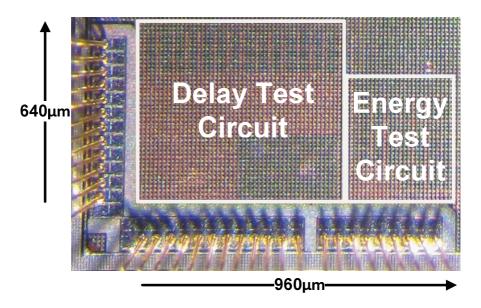

| 7.5  | Micrograph of the test circuit for novel CSEs and TGPL                     | 216 |

| 7.6  | Layout of the test circuit for novel CSEs and TGPL                         | 216 |

| 7.7  | Block diagram of delay and energy measurement circuits                     | 217 |

| 7.8  | Setup (a-b) and Hold (c-d) timing characteristics of CP <sup>3</sup> L,    |     |

|      | CSP <sup>3</sup> L and TGPL                                                | 221 |

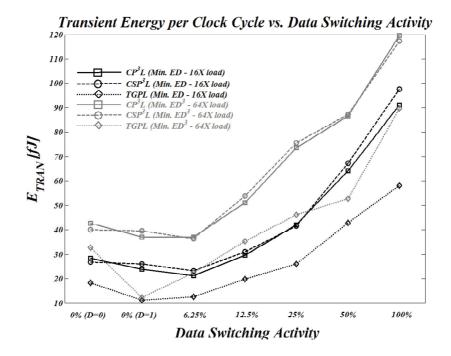

| 7.9  | Transient energy vs. switching activity                                    | 222 |

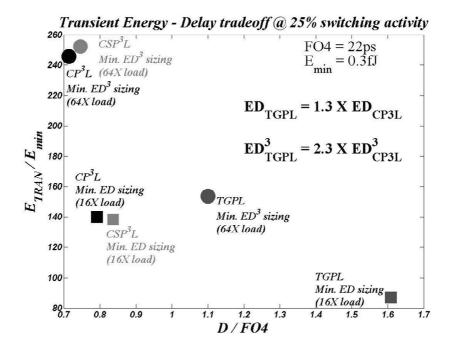

| 7.10 | Energy-delay tradeoff                                                      | 223 |

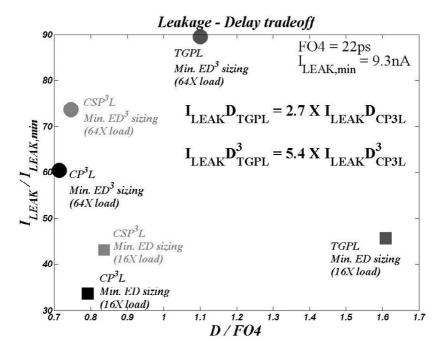

| 7.11 | Leakage-delay tradeoff                                                     | 223 |

| 7.12 | Variability of timing parameters and leakage                               | 224 |

List of Tables XXI

# LIST OF TABLES

| I.I           | Logical effort and parasitic delay for NAND and NOR gates having <i>M</i> inputs and <i>S</i> rise/fall skew             | 16  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| II.I          | 4-bit RCA: minimum $E^iD^j$ designs                                                                                      | 52  |

| IV.I<br>IV.II | SDFF LE parameters: stage $S = [1,2,3]$ / path $P = [r,f]$<br>Properties of the minimum $E^iD^j$ designs for the SDFF in | 110 |

|               | presence and in absence of local wires' parasitics inclusion                                                             | 112 |

| IV.III        | Parasitic capacitances estimation in SDFF                                                                                | 118 |

| IV.IV         | LE parameters for the TGFF considered as a whole path (from                                                              |     |

|               | $D \text{ to } \overline{Q}) \text{ with } N = 3 \text{ stages.}$                                                        | 125 |

| IV.V          | LE parameters for the TGFF considered as the union of two                                                                |     |

|               | paths each with $N = 2$ stages                                                                                           | 125 |

| IV.VI         | Error between min. $ED^4$ sizings extracted with                                                                         |     |

|               | traditional/proposed procedures and an optimization algorithm                                                            | 130 |

| IV.VII        | Sizing, Energy and Delay for the proposed procedure, min.                                                                |     |

|               | ED <sup>4</sup> and min. ED sizings in some reference cases                                                              | 130 |

|               | Ç .                                                                                                                      |     |

| V.I           | Analysis of the sensitivity $S_D^E$                                                                                      | 143 |

| V.II          | TGFF sizing for $T_{CK}/FO4 = 10$ and $T_{CK}/FO4 = 80$                                                                  | 165 |

| V.III         | Optimum sizing variation for $T_{CK}/F04 = 10$ and                                                                       |     |

|               | $T_{CK}/F04 = 80$                                                                                                        | 165 |

| V.IV          | Average leakage (normalized to the minimum is reported in                                                                |     |

|               | brackets) under various optimum sizing and average (among                                                                |     |

|               | the FOMs) ratio between average and minimum leakage                                                                      | 166 |

XXII List of Tables

| V.V    | Absolute area under various optimum sizing (area normalized to the minimum is reported in brackets) in the first three columns                                       |     |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | Layout efficiency under various optimum sizing in the last eight columns                                                                                             | 170 |

| V.VI   | Clock load under various optimum sizing (clock load normalized to the minimum is reported in brackets) and average (among the FOMs) percentage contribution of clock |     |

|        | wires                                                                                                                                                                | 174 |

| V.VII  | Percentage energy increment due to a clock tapered buffer                                                                                                            |     |

|        | driving $M = 128$ CSEs (normalized to CSEs energy, $ME_{CSE}$ ).                                                                                                     | 177 |

| VI.I   | Parameters a and b (sizings for minimum $ED$ , $ED^3$ , $E^3D$ )                                                                                                     | 189 |

| VI.II  | Predicted and simulated energy of a tapered buffer                                                                                                                   | 192 |

| VI.III | Adopted scaling factors to model next technology generations.                                                                                                        | 207 |

| VI.IV  | Optimum clock slope at various technology generations                                                                                                                | 207 |

| VII.I  | Novel CSEs comparison with TGPL, TGFF, ACFF, STFF                                                                                                                    | 225 |

Introduction 1

### INTRODUCTION

The design of the clock network represents a crucial aspect when dealing with CMOS VLSI integrated circuits, as it strongly affects not only the chip speed, but also its overall energy consumption.

Independently from the basic nature (fully synchronous, globally asynchronous locally synchronous) of the systems where it is employed, any clock network can be subdivided into three main parts. Indeed, similarly to the structure of a tree, we can identify a root constituted by the circuits devoted to clock generation, branches constituted by the wires and circuits devoted to clock distribution and, as the final leaves, the clocked storage elements, i.e. latches and flip-flops.

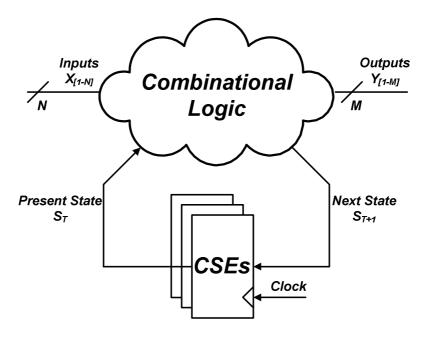

In particular, clocked storage elements are among the most important elements in the design of digital systems, such as microprocessors. They separate the various stages which a pipeline is made up by, maintain the present logic state and prevent the transition towards a new one until the "right" instant occurs. On the whole, they allow to synchronize and regulate the entire flow of digital data within the system.

With the aim of obtaining conspicuous performance increments at each process generation, dimensional scaling has been supported by the reduction of the number of logic stages (logic depth) within each pipeline stage. Therefore, an increasing impact of the timing overhead due to clocked storage elements on the clock period can be observed. On the other hand, due to the high switching activity featuring clocked gates, the overall dissipation of the clock network can be as high as 30-50% of the overall chip energy budget. Moreover, the fraction of this contribution due to clocked storage elements tends to increase again due to the decreasing logic depth and, in some cases, because of the adoption of novel low energy clock distribution techniques.

2 Introduction

The above issues, together with the needs for an high operation robustness and for the capability to deal with clock signal uncertainties, make the clocked storage elements design a key aspect in the VLSI systems domain, and, in order to account for all the mentioned aspects, it may be also quite complex. For this reason, these circuits have been extensively studied in the past and a significant effort has been devoted to provide guidelines for the identification of new circuital solution and the selection of the most suitable clocked storage elements according to the requirements of the application.

Moreover, the task of carrying out topologies selection and optimized design strategies is now made more complicated since two main challenges arise when adopting the current technologies: the increasing relevance of energy consumption and the effects arising at nanometer scale.

In particular, the continuous increase in energy consumption (due to the raising impact of leakage dissipation) has become the major concern limiting the speed performances of digital VLSI integrated circuits, insomuch as, even for high-speed systems, designs undergo a so-called power limited regime. Therefore, since the achievement of energy-efficiency must be the primary target, a deep understanding of the energy-delay tradeoff and the related design issues is crucial.

Secondly, when entering the nanometer scale, several effects have to be considered, such as the impact of layout parasitics associated with interconnects, degrading both speed and energy, and leakage, affecting energy both in active and in standby operation modes. Such effects, which once could be neglected, have now become prominent.

The topics of energy-efficient design, analysis, comparison and selection of suitable clocked storage elements topologies for applications in nanometer technologies have been the focus of the research activity carried out by the candidate in pursuit of the Ph.D. degree. The aim of this thesis is to provide a deep understanding of the challenges relative to clocked storage elements design and selection when including all the above mentioned aspects, as well as to propose novel energy-efficient solutions at the transistor- and microarchitectural design levels. This target is accomplished by organizing the candidate's recent results as well as the other ones reported in the literature.

The basic theoretical foundations are provided to set the stage for the comprehension of analyses and results. Exhaustive methodologies are presented and many analytical derivations are included, since they allow to gain an insight on the main dependencies of relevant parameters on circuital properties. Finally, several results, which have been derived by carrying out extensive simulation analyses and measurements on an integrated chip prototype are reported to emphasize the practical perspective of the work.

Introduction 3

The outline of the work is as follows.

The first three chapters contain all the basic theoretical elements, including some novel results, that are exploited in the remaining part of the book. Chapter 1 describes the well known Logical Effort method, which is extensively adopted throughout the book, both as a modeling approach and as a methodology to design circuits for delay minimization. It is shown that, when designing digital circuits in the energy-delay space, Logical Effort method allows to derive practical design constraints.

Chapter 2 reports consideration on the energy consumption of digital circuits and the theory concerning their efficient design in the energy-delay space. The adoption of suitable figures of merit and the concept of energy-efficient curve are discussed, since they are exploited when deriving a novel optimization methodology that takes into account the energy-delay tradeoff.

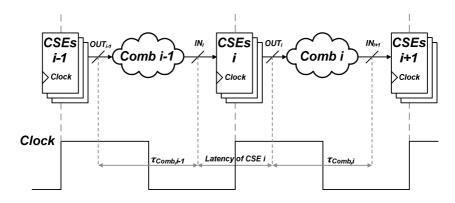

Chapter 3 provides an overview of clocking and clocked storage elements operation and of the main parameters related to their timing and energy features. The main topological classes are presented, together with their basic properties.

A detailed and extensive design strategy for nanometer CMOS clocked storage elements through circuital optimization in the energy-delay space is presented in Chapter 4. The methodology accounts for the impact of parasitics due to interconnects, which strongly increases in nanometer technologies, and widely exploits the theories of Logical Effort and of energy-efficient design described in the first two chapters.

The results of a wide comparison among 19 clocked storage elements topologies, selected among the most representative and best known previously proposed ones, are reported in Chapter 5. Besides the exploration of the energy-delay one, several other tradeoffs involving leakage, area and clock load are investigated, thereby allowing to compare clocked storage elements in a more general framework.

Chapter 6 contains novel results concerning the optimization of clock distribution at the clock domain level. The energy-delay tradeoff is again examined by observing the joint performances of clock buffers and clocked storage elements when locally varying the clock slope.

Novel ultra-fast clocked storage elements topologies are presented in Chapter 7, together with measurements results extracted from a chip prototype in a 65-nm CMOS technology. These novel circuits belong to the Pulsed Latches class, which, from the analysis in Chapter 5, is recognized as the most promising one in nanometer technologies. Overall, the proposed topologies achieve the best speed and energy-efficiency performances in the high-speed energy-delay region that have ever been reported.

Finally, conclusions of the work are reported.

## Chapter 1

### THE LOGICAL EFFORT METHOD

This chapter describes the Logical Effort approach [SSH98], which represents the state of the art as concerns the modeling and optimization of CMOS digital circuits from the point of view of their speed performances. Such a methodology is often exploited throughout the following chapters, especially when dealing with the optimized clocked storage elements sizing and when searching for practical design space bounds.

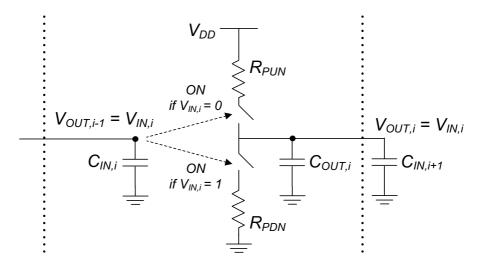

### 1.1 An RC Model for the Delay of Logic Gates

When searching for a model of the delay of logic gates, it is necessary to recur to some simplifications that can allow the development of back-of-the-envelope though useful calculations. From their basic structure and except for some cases, it is evident that CMOS logic gates can be simply modeled as decoupled RC blocks [H84]. As shown in Fig. 1.1, each block consists of supply( $V_{DD}$ )-to-output and ground-to-output alternately activated resistive paths, corresponding to pull-up (PUN) and pull-down (PDN) networks, respectively, and the output is capacitively self-loaded and externally loaded. Whether the PUN or PDN is activated depends on the logic value stored at the output of the previous block, whose external load is the input capacitance of the gate corresponding to the considered block. Hence, once suitable R and C values are found, an effective model for the delay estimation of CMOS logic gate can be easily developed.

The equivalent resistance R of a MOS can be evaluated by averaging out the derivative  $(\partial I_D/\partial V_{DS})^{-1}$  in the voltage range of interest. Anyhow, the most important consideration is that, independently from working in triode or saturation, the resistance of a MOS transistor is inversely proportional to

Fig. 1.1. CMOS logic gates seen as decoupled *RC* blocks.

its width W (for simplicity, by neglecting the impact of normal and reverse narrow width effects [CH99]). When considering complex CMOS gates, the evaluation of the total equivalent resistance of PUN and PDN can be approximately performed by summing the resistances of stacked blocks of transistors and by summing the conductances (which are proportional to W) of parallel blocks of transistors that are conducting the current at the same time [RCN03].

The equivalent capacitance at the input of a MOS transistor,  $C_G$ , can be evaluated by averaging out the sum of  $C_{GS}$  (gate-source),  $C_{GD}$  (gate-drain) and  $C_{GB}$  (gate-bulk) contributions in the voltage range of interest. The resulting value is proportional to WL and typically nearly equal to  $C_{ox}WL$  (being  $C_{ox}$  the gate oxide capacitance per unit area) [RCN03].

The self-loading in a CMOS gate is due to the drain-bulk (and source-bulk in internal nodes for stacked transistors) diffusion capacitances. Such capacitances can be expressed as [OK06]<sup>1</sup>

$$C_D = C_{D,A}WL_d + C_{D,P}(2W + 2L_d)$$

(1.1)

where  $L_d$  is the length of drain/source diffusions and  $C_{D,A}$  ( $C_{D,P}$ ) are the capacitances per unit area (perimeter) of drain-bulk and/or source-bulk

<sup>&</sup>lt;sup>1</sup> Note that sometimes the sidewall capacitance is not counted for the side of diffusion adjacent to the channel [RCN03]. In this case, the second term of equation (1.1) becomes equal to  $C_{D,P}(W + 2L_d)$ .

junctions, evaluated by averaging out in the voltage range of interest<sup>2</sup>. By neglecting the  $2L_dC_{D,P}$  term,  $C_D$  can be considered nearly proportional to W.

Summarizing, by considering

- a) a CMOS gate with all stacked transistors of the same size;

- b) only one conductive branch among the existing ones;

- c) a constant ratio between the size of PMOS and NMOS; one has that

$$C_{IN} \propto WL$$

(1.2a)

$$C_{OUT} \propto W$$

(1.2b)

$$R_T \propto L/W$$

(1.2c)

where  $C_{IN}$  is the input capacitance of the gate terminal where the critical input is applied,  $C_{OUT}$  is the total diffusion capacitance at the output (also including contributions from internal nodes) and  $R_T$  is the resistance of PUN or PDN.

Usually, the channel lengths are all minimum, and the considered gate can be seen as a version scaled by a factor  $\alpha$  (in terms of channel width) of a reference gate of the same type, called the "template" gate (typically considered of minimum size). Such a gate exhibits parameters  $C_{IN,ref}$ ,  $C_{OUT,ref}$  and  $R_{T,ref}$  and the following relationships hold [OK06]

$$C_{IN} = \alpha C_{IN,ref} \tag{1.3a}$$

$$C_{OUT} = \alpha C_{OUT,ref} \tag{1.3b}$$

$$R_T = R_{T,ref}/\alpha \tag{1.3c}$$

Hence, any timing parameter of the considered gate can be expressed as [H84]

$$t_D = KR_T(C_{OUT} + C_L) = K\left(R_{T,ref}C_{IN,ref}\frac{c_L}{c_{IN}} + R_{T,ref}C_{OUT,ref}\right) (1.4)$$

$$K_j = \frac{\phi^m}{V_2 - V_1} \left[ \frac{(\phi - V_1)^{1-m}}{1 - m} - \frac{(\phi - V_2)^{1-m}}{1 - m} \right]$$

where  $\phi$  is the built-in potential across the junction, m is the grading coefficient of the junction, and  $V_1$  and  $V_2$  are the minimum and maximum direct voltages across the junction, respectively [RCN03].

$C_{D,P}$  is equal to  $C_{D,A}x_j$ , being  $x_j$  the depth of the diffusion.

<sup>&</sup>lt;sup>2</sup> By considering the large signal behavior of reverse-biased junction capacitances,  $C_{D,A}$  can be equaled to  $C_{j0}K_j$ , being  $C_{j0}$  the value under zero bias condition, and

where  $C_L$  is the external output load and K depends on the kind of timing parameter (delay, fall/rise times) and on the slope of the input. For instance, when considering the propagation delay under a step input, K = 0.69.

An equivalent model can be derived considering the current provided by the gate instead of equivalent resistances (see the short Appendix at the end of this chapter).

It is worth noting that especially the evaluation of equivalent resistances requires several approximations to manage the various effects arising in deep-submicron technologies and influencing the I-V behavior of MOS transistors. Some of these effects are mobility degradation, carriers velocity saturation, channel length modulation, drain-induced barrier lowering (DIBL), short-channel and narrow-width effects (e.g.,  $V_{TH}$  roll-off) and so on (see [T03] and [TN09] for a thorough discussion).

For instance, according to a well-known short-channel model [TKM88], the classic inversely proportional dependence of MOS current from channel length L is damped because of velocity saturation, i.e.

$$I_D \propto \begin{cases} \frac{1}{V_{DS} + LE_{cr}} & in \ triode \ region \\ \frac{1}{(V_{GS} - V_{TH}) + LE_{cr}} & in \ saturation \ region \end{cases}$$

(1.5)

where  $V_{TH}$  is the threshold voltage and  $E_{cr}$  is the electrical field for which velocity saturation is observed. Meanwhile, due to short-channel effects,  $V_{TH}$  decreases when lowering L [Y74]. Hence, on the whole, an  $R \propto L$  approximation is still feasible.

Another example is given by the case of n stacked MOS transistors, which classically exhibit a total equivalent resistance equal to nR, being R that of a single transistor. When considering velocity saturation, this effect again grows fainter since transistors enter current saturation for smaller voltages [SN91]. Meanwhile, channel length modulation and DIBL effects have a severe impact and increase the dependence of saturation current from  $V_{DS}$ .

## 1.2The Logical Effort Model

The RC model in (1.4) was revisited in [SSH98] to obtain a new one normalized to (i.e., independent from) technology: the Logical Effort model. Basically, formula (1.4) is divided by  $R_{INV}C_{INV}$ , which is the product of the equivalent resistance and input capacitance of a symmetrical inverter, i.e. an inverter showing symmetric PUN and PDN driving capabilities (in current technologies, this is typically obtained by sizing the PMOS twice the size of

the NMOS). Note that, even if the absolute size of this inverter is varied, the product  $R_{INV}C_{INV}$  is a constant dependent on technology.

Once normalized, the timing parameter of the considered gate,  $t_D$ , (which in the following is referred as delay without loss of generality) becomes

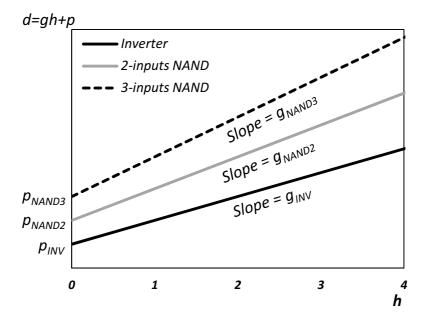

$$t_D = \tau(gh + p)$$

$$t_D = \tau(f + p) = \tau d$$

(1.6a)

(1.6b)

$$t_D = \tau(f + p) = \tau d \tag{1.6b}$$

where the various quantities correspond to

$$\tau = KR_{INV}C_{INV} \tag{1.7}$$

$$g = \frac{R_{T,ref}C_{IN,ref}}{R_{INIV}C_{INIV}} \tag{1.8}$$

$$h = \frac{c_L}{c_{IN}} \tag{1.9}$$

$$\tau = KR_{INV}C_{INV}$$

$$g = \frac{R_{T,ref}C_{IN,ref}}{R_{INV}C_{INV}}$$

$$h = \frac{C_L}{C_{IN}}$$

$$p = \frac{R_{T,ref}C_{OUT,ref}}{R_{INV}C_{INV}}$$

(1.7)

(1.8)

(1.9)

The parameter  $\tau$  allows to normalize the absolute delay  $t_D$  to technology and it represents the delay of symmetrical inverter loaded with an inverter of the same size and neglecting the self-loading due to diffusion capacitances.

The parameter g is called "Logical effort" and, except for some cases, is a feature dependent on the gate's topology and hence not affected by the "absolute" sizing of the gate but only by its "relative" sizing (by definition, g = 1 for a symmetrical inverter).

The logical effort g describes the driving capability of the gate topology and has a twofold interpretation:

- 1) under the assumption of equal  $C_{IN}$ , g indicates how much worse is the driving capability of the considered gate with respect to that of a symmetrical inverter;

- 2) under the assumption of equal driving capability, g indicates how much larger the considered gate has to be (in terms of  $C_{IN}$ ) with respect to a symmetrical inverter.

The parameter h is called "Electrical effort" and it is equal to the fanout of the gate. It is independent from the topological characteristics of the gate, is affected only by the absolute gate sizing (i.e., it depends on  $\alpha$ ) and affects the normalized delay d as much as g. Obviously it increases for high  $C_L$ (heavier load) and decreases for high  $C_{IN}$  (larger driving capability).

The parameter p is called "Parasitic delay" and represents the intrinsic and unavoidable delay contribution due to the self-loading of the gate. As for g, except for some cases, p is a feature dependent on the gate's topology and hence it is not affected by the "absolute" sizing of the gate but only by its "relative" sizing. Indeed when enlarging the gate size to improve its driving capability, also the capacitance  $C_{OUT}$  increases proportionally. In the case of an inverter, p is close to 1, since typically  $C_G \approx C_D$ .

Finally, the parameters f (equal to gh) and d are named "Stage effort" and "Normalized delay", respectively.

It is apparent that the normalized delay d is a linear function of h, as shown in Fig. 1.2. The logical effort g represents the slope of such a line, whereas the parasitic delay p is the minimum achievable delay extrapolated for h = 0, i.e. for zero external load or for  $C_{IN} \gg C_{L}$ .

Fig. 1.2. Geometrical interpretation of logical effort and parasitic delay.

# 1.3 Limitations of the Original Logical Effort Model

The model described so far recurs to several simplifications and suffers from some limitations, which, however, appears necessary when trying to develop back-of-the-envelope calculations.

The model assumes MOS transistors behaving as equivalent resistances. However, for the major part of the transient state in the case of rise/fall times and always in the case of delays, MOS transistors behave as non ideal current generators. Such a phenomenon arises in deep submicron technologies, since the drain-to-source saturation voltage decreases with respect to the classic behavior [RCN03]. Anyhow, the results maintain their validity since the dependence from channel widths and lengths is basically