Dottorato di Ricerca in Ingegneria dei Sistemi, Energetica, Informatica e delle Telecomunicazioni XXIX Ciclo

#### LEANDRO GRASSO

# RF Harvesting System for Remotely Powered Wireless Sensor Nodes

| Ph.D. Thesis        |                               |

|---------------------|-------------------------------|

| Tutor:<br>Ch.mo P   | rof. Ing. Giuseppe Palmisano  |

| Coordina<br>Ch.mo P | tor:<br>rof. Ing. Paolo Arena |

Academic Year 2015-2016

## **Table of Contents**

| Acknowledgeme   | ents                                        | X  |

|-----------------|---------------------------------------------|----|

| Abstract        |                                             | xi |

| Chapter I: Ener | rgy harvesting for wireless sensor networks | 1  |

| 1.1 Wir         | reless sensor networks                      | 1  |

| 1.1.1           | Applications                                | 3  |

| 1.2 Ene         | ergy harvesting                             | 5  |

| 1.2.1           | Vibration harvesting                        | 5  |

| 1.2.2           | 2 Thermal harvesting                        | 6  |

| 1.2.3           | Photovoltaic harvesting                     | 7  |

| 1.2.4           | Radio-frequency harvesting                  | 8  |

| 1.2 RF          | harvesting systems                          | 10 |

| 1.2.1           | Rectifier                                   | 11 |

| 1.2.2           | 2 Antenna                                   | 16 |

| 1.2.3           | B Design constraints                        | 17 |

| Referen         | 1ces                                        | 22 |

| Chapter II: C | CMOS differential-drive rectifier2         | 26 |

|---------------|--------------------------------------------|----|

| 2.1 (         | Operating principle                        | 26 |

| 2.2 F         | Proposed topology                          | 30 |

| 2.3 F         | Rectifier model                            | 35 |

| Refer         | rences2                                    | 10 |

|               |                                            |    |

| Chapter III:  | Antenna 2                                  | 11 |

| 3.1 F         | Proposed ICL antenna                       | 11 |

| Refer         | rences2                                    | 15 |

|               |                                            |    |

| Chapter IV:   | Co-design methodology                      | 16 |

| 4.1 (         | General outline2                           | 16 |

| 4.2 F         | Rectifier design2                          | 17 |

| 4.2           | 2.1 Technology-dependent design parameters | 18 |

| 4.2           | 2.2 Voltage-drop estimation                | 18 |

| 4.2           | 2.3 Number of stages                       | 19 |

| 4.2           | 2.4 Transistor width                       | 19 |

| 4.2           | 2.2 Pumping capacitors                     | 51 |

| 4.2           | 2.3 Topology improvement                   | 52 |

| 4.2           | 2.4 Maximum allowable quality factor       | 52 |

| 4.1 (         | Co-design approach5                        | 53 |

| References6                        | 50        |

|------------------------------------|-----------|

| Chapter V: Measurement methods 6   | 51        |

| 5.1 Rectifier measurement methods  | 51        |

| 5.2.1 Three-loads method           | 53        |

| 5.2.2 Three-ports method           | 54        |

| 5.2 Antenna measurement methods    | 59        |

| 5.2.1 Impedance measurement        | 59        |

| 5.2.2 Efficiency measurement       | 73        |

| References                         | <b>78</b> |

|                                    |           |

| Chapter VI: Experimental results 8 | 30        |

| 6.1 Rectifier                      | 30        |

| 6.2 Antenna 8                      | 32        |

| 6.2 Overall system                 | <b>37</b> |

| References 8                       | 39        |

|                                    |           |

| Conclusions9                       | 90        |

| Appendix 9                         | 92        |

## **List of Figures**

### Chapter I

| Fig. 1.1.  | Scheme of a generic wireless sensor network.                         | 1  |

|------------|----------------------------------------------------------------------|----|

| Fig. 1.2.  | Block diagram of a generic wireless sensor node.                     | 2  |

| Fig. 1.3.  | Power requirements and lifetime of typical WSN products.             | 3  |

| Fig. 1.4.  | Passive RFID tag and reader.                                         | 4  |

| Fig. 1.5.  | RF harvesting for remotely-powered switch.                           | 5  |

| Fig. 1.6.  | Experimental prototype of tri-stable magnetically-coupled cantilever | S  |

| having pie | zoceramic elements as active materials                               | 6  |

| Fig. 1.7.  | Artwork of a thermoelectric microsystem.                             | 7  |

| Fig. 1.8.  | Scheme of a generic photovoltaic harvesting system.                  | 8  |

| Fig. 1.9.  | Power propagation scheme between wireless sensor nodes               | 10 |

| Fig. 1.10. | Schematic of the half-wave rectifier.                                | 11 |

| Fig. 1.11. | Schematic of the full-wave rectifier.                                | 12 |

| Fig. 1.12. | Schematic of the Graetz Bridge.                                      | 13 |

| Fig. 1.13. | Schematic of a Dickson multi-stage rectifier.                        | 14 |

| Fig. 1.14. | Schematic of the Dickson-based self compensation topology            | 15 |

| Fig. 1.15. | Schematic of the CMOS differential-drive rectifier                   | 15 |

| Fig. 1.16. | Schematic of the CMOS differential-drive rectifier with auxiliary    |    |

| PMOS       |                                                                      | 16 |

| Fig. 1.17. | Layout of a generic T-match antenna                                  | 17 |

| Fig. 1.18.   | Layout of a generic inductively couple loop (ICL) antenna              | 18     |

|--------------|------------------------------------------------------------------------|--------|

| Fig. 1.19.   | Simplified representation of an RF harvesting system.                  | 19     |

| Fig. 1.20.   | Simplified impedance model of a RF harvesting system                   | 21     |

|              |                                                                        |        |

| Chapte       | r II                                                                   |        |

| Fig. 2.1.    | Schematic of the single-stage CMOS differential-drive                  | 27     |

| Fig. 2.2.    | Schematic of the multi-stage CMOS differential-drive.                  | 27     |

| Fig. 2.3.    | Typical voltage waveforms in internal nodes, X and Y, of the first     | t      |

| stage of a   | CMOS differential-drive rectifier.                                     | 27     |

| Fig. 2.4.    | Schematic of the generic $n^{th}$ -stage with the proposed improvement | t 31   |

| Fig. 2.5.    | Steady-state pumping current of the proposed and classic               |        |

| rectifier st | age                                                                    | 34     |

| Fig. 2.6.    | Simplified example with $i = -j = 1$ of the proposed CMOS              |        |

| differentia  | al-drive rectifier with body voltage control                           | 35     |

| Fig. 2.7.    | Linear model of a single-stage full-wave rectifier.                    | 36     |

| Fig. 2.8.    | Simulated input resistance of the single-stage rectifier versus trans  | sistor |

| W for diffe  | Ferent $C_p$ values                                                    | 37     |

| Fig. 2.9.    | Simulated input capacitance of the single-stage rectifier versus       |        |

| transistor   | $W$ for different $C_p$ values.                                        | 38     |

| Fig. 2.10.   | Simulated quality factor of the single-stage rectifier versus tran     | sistor |

| W for diff   | erent $C_p$ values                                                     | 38     |

## Chapter III

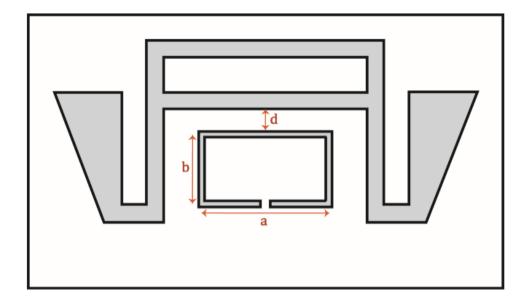

| Fig. 3.1.        | Layout of the proposed inductively coupled loop antenna                              |

|------------------|--------------------------------------------------------------------------------------|

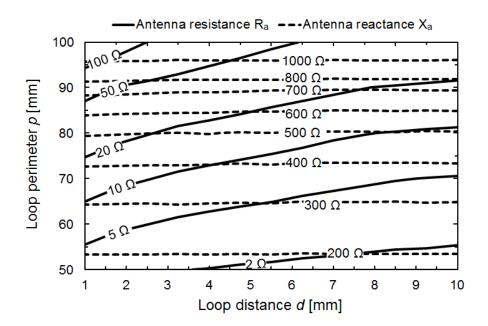

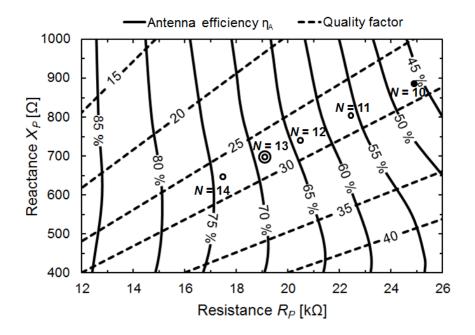

| Fig. 3.2.        | Simulated level curves showing series resistance $R_a$ and reactance $X_a$           |

| of the prop      | posed ICL antenna. 43                                                                |

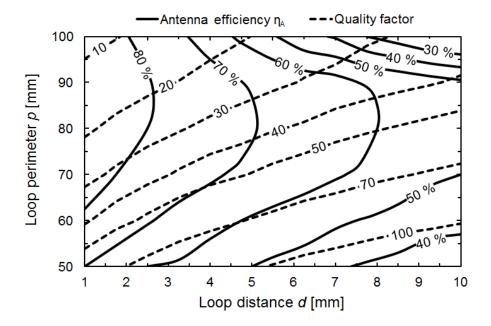

| Fig. 3.3.        | Simulated level curves showing efficiency $\eta_A$ and quality factor $Q$ of         |

| the propos       | sed ICL antenna. 43                                                                  |

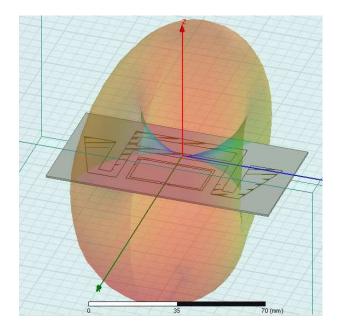

| Fig. 3.4.        | Radiation pattern of the proposed ICL antenna                                        |

|                  |                                                                                      |

| Chapte           | r IV                                                                                 |

| Fig. 4.1.        | Proposed design flow for the differential-drive rectifier                            |

| Fig. 4.2.        | Simulated curves of $V_{on}$ versus $V_{in}$ at different couples of width and       |

| pump capa        | acitance values for a single-stage CMOS full-wave rectifier ( $V_{out} = 240$        |

| $mV, I_L =$      | 1 μΑ)                                                                                |

| Fig. 4.3.        | Rectifier efficiency evaluated at different load currents                            |

| $(V_{out} = 240$ | 0 mV)                                                                                |

| Fig. 4.4.        | Simulated curves of $\eta_R$ versus $V_{in}$ at different width values for a single- |

| stage CM0        | OS full-wave rectifier ( $V_{out} = 240 \text{ mV}$ , $I_L = 1  \mu\text{A}$ )       |

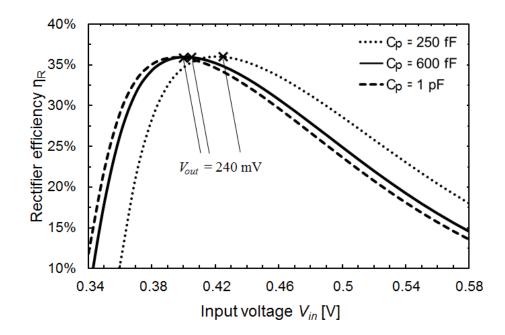

| Fig. 4.5.        | Simulated curves of $\eta_R$ versus $V_{in}$ at different pump capacitance values    |

| for a singl      | e-stage CMOS full-wave rectifier ( $V_L = 240 \text{ mV}, I_L = 1  \mu\text{A}$ )    |

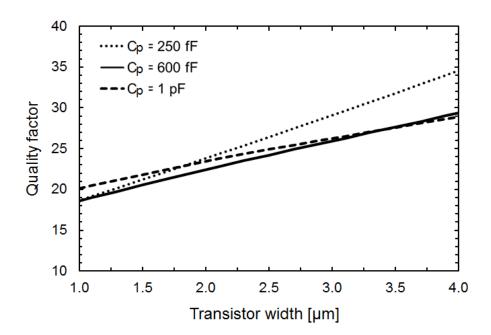

| Fig. 4.6.        | Simulated curves of $Q$ versus $W$ at different pump capacitance values              |

| for a singl      | e-stage CMOS full-wave rectifier ( $V_L = 240 \text{ mV}, I_L = 1 \mu\text{A}$ )     |

| Fig. 4.7.        | Antenna matching chart adopted in the proposed co-design                             |

| methodolo        | ogy                                                                                  |

| Fig. 4.8.   | Antenna matching chart adopted in design A.                             | 57    |

|-------------|-------------------------------------------------------------------------|-------|

| Fig. 4.9.   | Antenna matching chart adopted in design B.                             | 58    |

| Fig. 4.10.  | Antenna matching chart adopted in design C.                             | 59    |

|             |                                                                         |       |

| Chapte      | er V                                                                    |       |

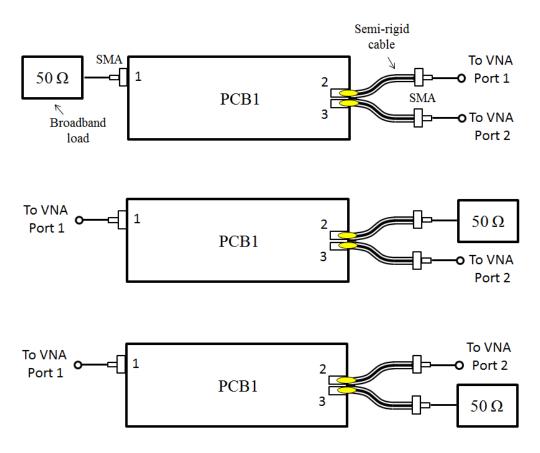

| Fig. 5.1.   | Scheme of the rectifier measurement setup.                              | 63    |

| Fig. 5.1.   | Three-loads measurement setup.                                          | 64    |

| Fig. 5.2.   | Three-ports measurement setup.                                          | 65    |

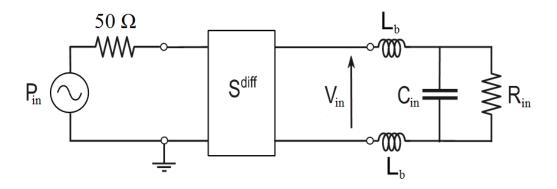

| Fig. 5.3.   | Scheme of the rectifier measurement setup.                              | 66    |

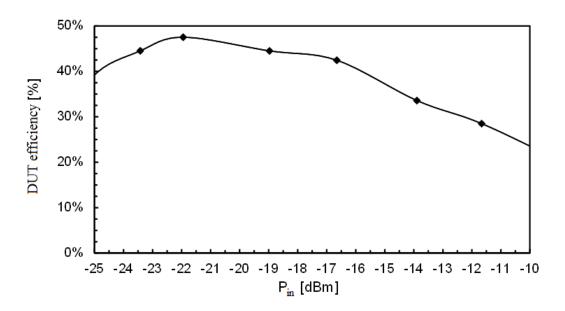

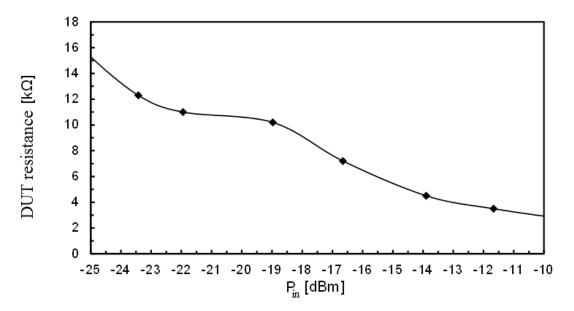

| Fig. 5.4.   | Calculated efficiency $\eta_R$ as a function of $P_{in}$                | 68    |

| Fig. 5.5.   | Calculated resistance $R_{in}$ as a function of $P_{in}$ .              | 68    |

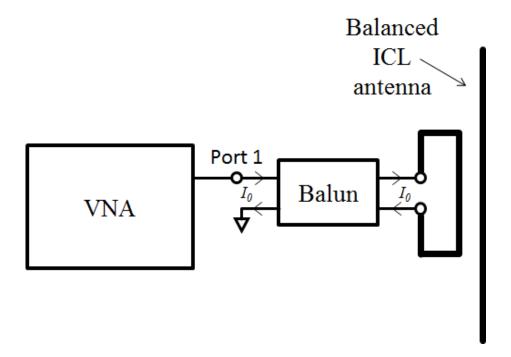

| Fig. 5.6.   | Measurement setup with balun.                                           | 70    |

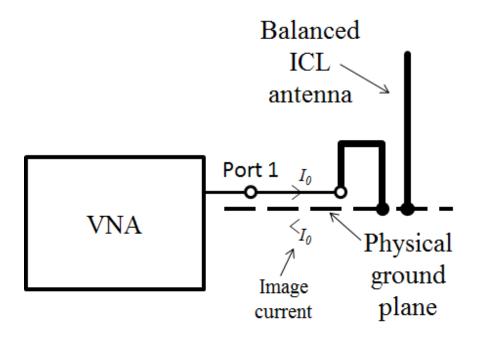

| Fig. 5.7.   | Half antenna soldered on a ground plane.                                | 70    |

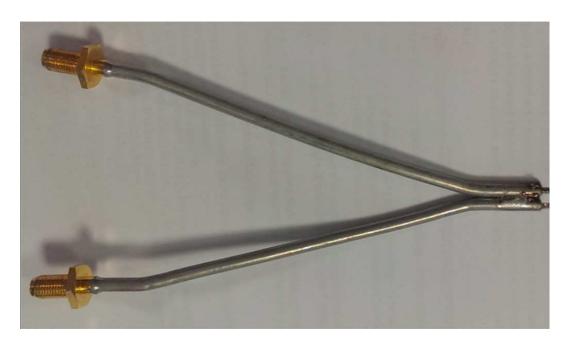

| Fig. 5.8.   | Test fixture (jig) adopted within the measurement setup                 | 71    |

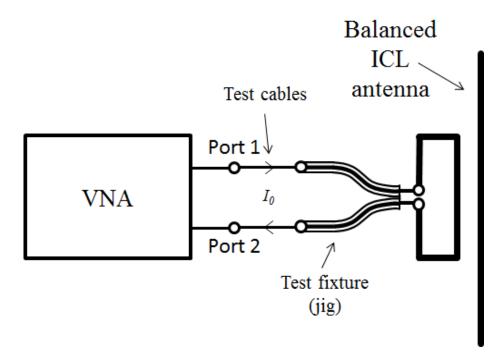

| Fig. 5.9.   | Measurement setup with jig.                                             | 72    |

| Fig. 5.10.  | Two-port network representation of the ICL antenna.                     | 72    |

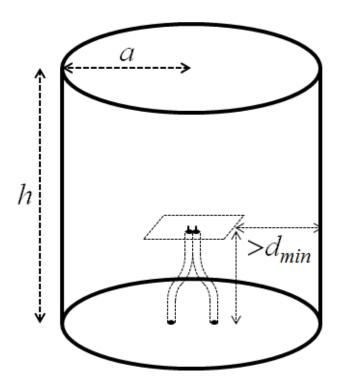

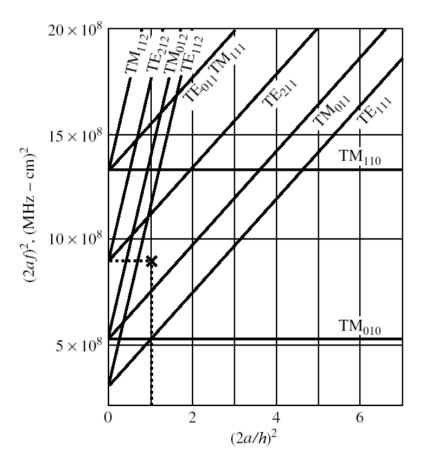

| Fig. 5.11.  | Cylindrical cavity used as Wheeler cap.                                 | 75    |

| Fig. 5.12.  | Resonant mode chart for the cylindrical cavity in Fig. 5.11             | 76    |

|             |                                                                         |       |

| Chapte      | r VI                                                                    |       |

| Fig. 6.1.   | Die microphotograph of the proposed rectifier                           | 81    |

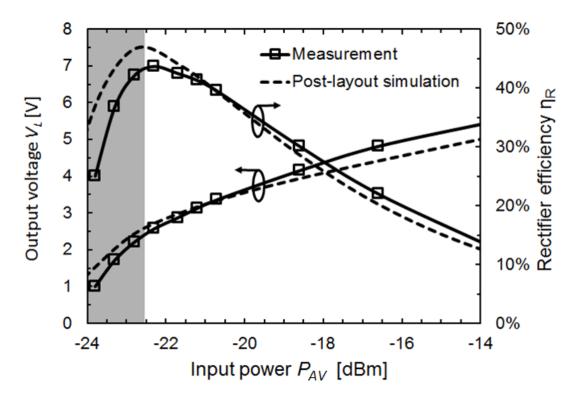

| Fig. 6.2.   | Measured and post-layout efficiency $\eta_R$ and output voltage $V_L$ v | ersus |

| available i | nput power $P_{4V}$                                                     | 82    |

| Fig. 6.3.       | Photograph of the fabricated ICL antenna.                                       | 83 |

|-----------------|---------------------------------------------------------------------------------|----|

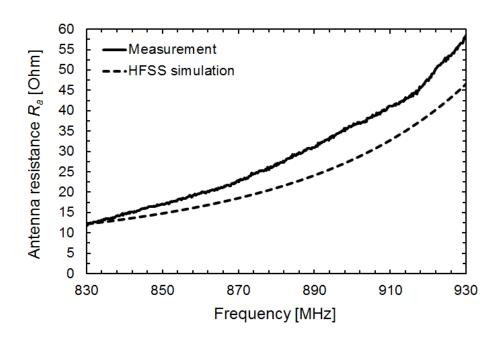

| Fig. 6.4.       | Measured and simulated resistance $R_a$ of the proposed ICL antenna             |    |

| versus free     | quency                                                                          | 83 |

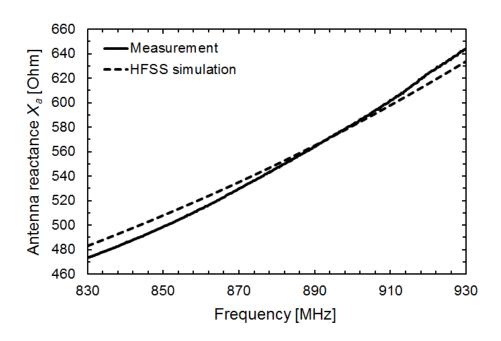

| Fig. 6.5.       | Measured and simulated reactance $X_a$ of the proposed ICL antenna              |    |

| versus frec     | quency                                                                          | 84 |

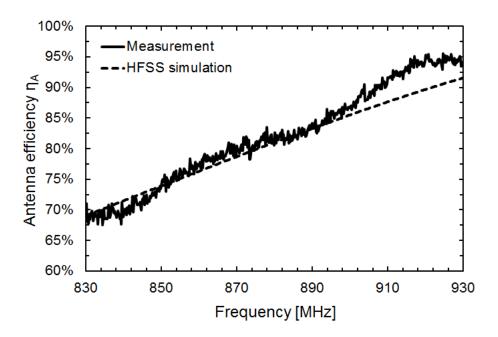

| Fig. 6.6.       | Measured and simulated efficiency $\eta_{\text{A}}$ of the proposed ICL antenna |    |

| versus frec     | quency                                                                          | 84 |

| Fig. 6.7.       | Antenna efficiency estimation with the Wheeler cap method                       | 85 |

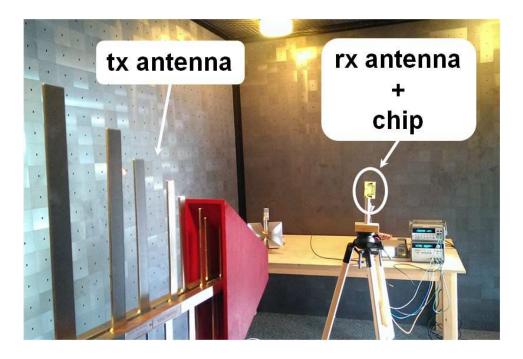

| Fig. 6.8.       | Measurement setup into the anechoic chamber.                                    | 85 |

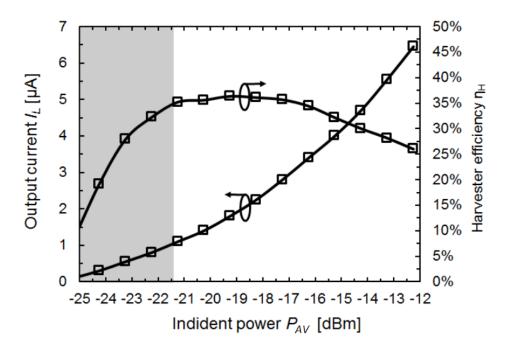

| Fig. 6.9.       | Measured efficiency $\eta_H$ and output current $I_L$ versus incident power     |    |

| $P_{AV}$ of the | proposed harvesting system, with $V_L = 2.4 \text{ V}.$                         | 86 |

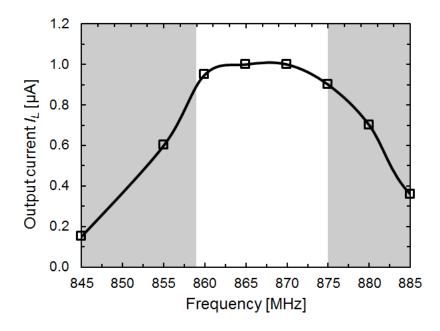

| Fig. 6.10.      | Measured output current $I_L$ versus frequency of the proposed                  |    |

| harvesting      | system, with $V_L = 2.4 \text{ V}.$                                             | 86 |

## **List of Tables**

| Chapter I                                                                      |

|--------------------------------------------------------------------------------|

| Γable 1.1. Frequency band restrictions for RFID applications                   |

|                                                                                |

| Chapter IV                                                                     |

| Table 4.1. Legend of the iteration circles shown in Fig. 4.8, Fig. 4.9, and    |

| Fig. 4.10                                                                      |

| Table 4.2. Simulated antenna and rectifier PCE along with expected overall PCE |

| within project A ( $V_L = 1.2 \text{ V}$ , $I_L = 1.2 \mu\text{A}$ )           |

| Table 4.3. Simulated antenna and rectifier PCE along with expected overall PCE |

| within project B ( $V_L = 2.4 \text{ V}$ , $I_L = 600 \text{ nA}$ ).           |

| Γable 4.4. Simulated antenna and rectifier PCE along with expected overall PCE |

| within project C ( $V_L = 2.4 \text{ V}$ , $I_L = 1  \mu\text{A}$ ).           |

|                                                                                |

| Chapter VI                                                                     |

| Table 6.1. Comparison between experimental results of the proposed harvesting  |

| system with the state-of-the-art solutions. 88                                 |

## Acknowledgements

I would like to thank my advisor, Prof. *Giuseppe Palmisano*. His experience has greatly helped to improve my scientific approach.

I thank Eng. *Ranieri Guerra*, whose meticulous attitude has always offered interesting viewpoints during these years. I also thank Eng. *Egidio Ragonese* for his numerous advice, which I have really appreciated. Many thanks to *Prof. Gino Sorbello* for his very kind contribution to carrying out the antenna design. I would also like to thank *Alessandro Castorina*, *Santo Leotta* and *Egidio De Giorgio* for their essential support during the experimental characterizations.

I am also very grateful to all of those at RF-ADC and STMicroelectronics, especially *Alessandro Finocchiaro*, *Nunzio Spina*, *Giovanni Girlando*, *Santo Smerzi*, *Vincenzo Fiore*, *Pierpaolo Lombardo*, *Nunzio Greco*, *Alessandro Parisi* and *Gianluca Pellecchia*. I thank them for their contribution to my professional growth and for being a huge source of distractions that made each day worth living. Special thanks to my friend *Giuseppe Papotto*, who has constantly helped me during these three years.

Finally, I would like to acknowledge my family for everything. Without their support, I would not have done half of the things I made. I dedicate this thesis to them.

Leandro Grasso

#### **Abstract**

Modern applications such as supply chain management and the Internet of Things (IoT) have addressed research efforts on improving the power efficiency in low power embedded devices. On the other hand, recent advances on ultra-low-power systems (1-100 μW) have enabled battery replacement with energy harvesters (or scavengers), which rely on external energy sources, such as vibration, solar, thermal, or the RF carrier of a power transmitter. Energy harvesting systems lead to further reduce complexity and costs for periodic maintenance. Among the harvesting approaches, RF solutions show the clear advantage of providing full controllable operation regardless environmental conditions. Unfortunately, propagation loss and relatively low harvester sensitivity greatly affect the operating distance of RF harvesting systems.

To this purpose, several circuit solutions have been recently proposed to increase RF-DC power conversion efficiency and input sensitivity, by exploiting Dickson-based charge pumps or CMOS differential-drive rectifiers. Although the power-up voltage of both topologies is affected by the transistor threshold voltage  $V_t$ , Dickson charge pumps generally exhibit lower efficiency because also the voltage drop across the transistor drain-source terminals must exceed  $V_t$ . To overcome this limitation, several approaches have been proposed, which perform threshold-voltage compensation. On the other hand, CMOS differential-drive rectifiers have an inherent threshold-voltage compensation topology that made

these solutions widely used in the last decade. Nevertheless, different techniques have been suggested to further enhance rectifier efficiency and sensitivity by reducing the reverse current in the rectifying stages, which is the main cause of efficiency limitation.

Although the differential-drive rectifier is a consolidate state-of-the-art solution, it is still difficult to draw up a complete design methodology, which clearly explains how to properly set design parameters to optimize performance for a given specification. Moreover, rectifiers cannot be designed without jointly consider the antenna. Indeed, the optimal operating point for the rectifier can result in a non-optimal operating point for the overall system, thus precluding best system efficiency to be achieved.

In this work, an effective co-design methodology for a harvesting system based on a CMOS differential-drive rectifier and an inductive coupled loop (ICL) antenna is discussed. It allows the overall system efficiency to be maximized for a given load and bandwidth specifications, which in turn means enhancing sensitivity as well. Moreover, the proposed co-design methodology was applied to an improved rectifier topology, which includes a body-voltage control strategy. It takes advantage of the voltage waveforms inherently generated by the circuit itself to dynamically vary the transistor threshold voltage. Finally, a relevant effort in terms of an accurate characterization of the harvesting system was paid, with a dedicated measurement set-up able to verify power efficiency and input impedance of antenna and rectifier.

This dissertation is organized as follows. In chapter I, after a brief overview about WSNs and their applications, main energy harvestings approach are

discussed. In particular, RF harvesting system is described along with related design constraints. The proposed rectifier and antenna are presented in chapter II and III, respectively. Then, an effective co-design methodology for RF harvesting systems is drawn up in chapter IV. Chapter V and VI report the measurement methods properly reshaped and the experimental results, respectively. Finally, conclusions are given in the last section.

This project was carried out within the RF-ADC (*Radio Frequency Advanced Design Center*), a joint research group supported by the University of Catania and *STMicroelectronics*.

## **Chapter I**

# **Energy harvesting for wireless sensor networks**

#### 1.1 Wireless sensor networks

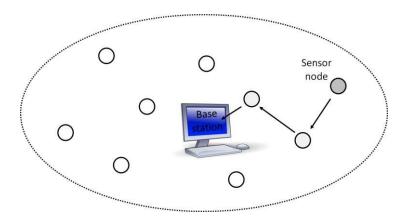

Wireless sensor networks (WSNs) mainly consist of a base station that communicates with several sensor nodes through a radio link, as shown in Fig. 1.1. Data is collected within each node, which re-transmits the processed information to the base station directly or via other nodes [1].

Fig. 1.1. Scheme of a generic wireless sensor network.

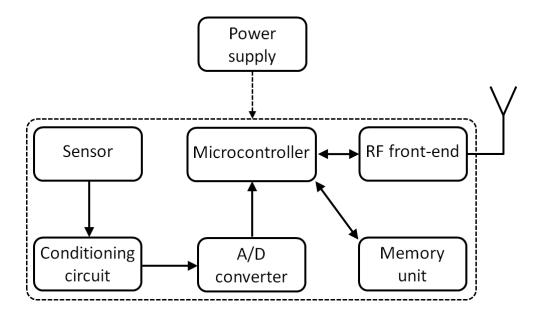

Fig. 1.2. Block diagram of a generic wireless sensor node.

Fig. 1.2 shows the block diagram of a generic wireless sensor node. As a first step, the *sensor* converts physical quantities into electric signals. Then, the signal is properly processed by an optional *conditioning circuitry* and converted into a digital signal by the *analog-to-digital converter*. The resulting digital signal goes to the *microcontroller* that manages the communications protocol, by interacting with the *RF front-end*. The latter processes the radio frequency signal coming from the antenna and can also perform the transmitting function. This block requires the largest amount of power, thus a duty-cycled operation is usually implemented [2]. A *memory unit* can be added to the system to store data from the base station or in correspondence of a particular event. Finally, the *power supply* circuitry manages the energy usually coming from a battery to supply the whole system. Although the battery energy density with respect to volume and weight has been substantially improved in the last decade, battery lifetime remains a crucial aspect within the increasingly smaller WSN devices.

#### 1.1.1 Applications

Nowadays, WSNs are adopted in different areas, such as health-care, lifestyle, automotive, smart buildings, active RFID tags, etc. These devices mainly suffer from limited lifetime, because of their substantial power requirement, which is shown in Fig. 1.3.

Fig. 1.3. Power requirements and lifetime of typical WSN products.

Unfortunately, long lifetime does not match up with the small form factor of these devices, since large batteries would usually be required. Then, energy harvesting approach has been adopted in recent years, by taking advantage of different environmental energy sources. This leads to increase node lifetime and make WSNs autonomous, thus cutting down costs related to supervision, configurations or maintenance. Some device can be made even completely autonomous by replacing the battery with the harvesting system, as happens for passive RFID tags [3]. These tags take advantage of the electromagnetic energy

coming from the reader to wake up the circuitry, thus receiving data and transmitting the information required (Fig. 1.4).

Fig. 1.4. Passive RFID tag and reader.

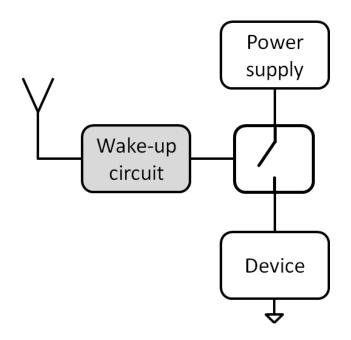

Fig. 1.5. RF harvesting for remotely-powered switch.

The RF circuitry can renounce transmitting functions, thus behaving as wake-up circuits only. As an example, among smart buildings applications, these circuits can be implemented to simply receive a code and then turning-on a remotely-powered switch that enable a generic device (Fig. 1.5) [4]. This results in cutting down power consumption related to stand-by mode in modern devices.

#### 1.2 Energy harvesting

As previously mentioned, several environmental energy source can be taken into account to increase node lifetime of wireless sensor nodes, such as vibrational, thermal, photovoltaic, and RF energy.

#### 1.2.1 Vibration harvesting

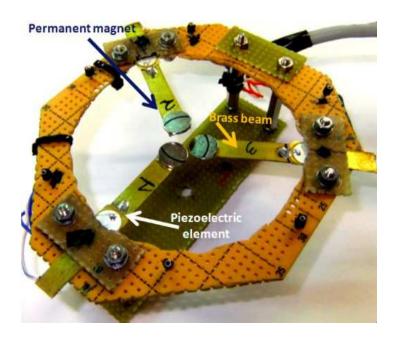

Vibration harvesting approach consists in adopting transduction mechanisms that convert motion to electric signals. These transducers are usually electrostatic, piezoelectric, or electromagnetic. Electrostatic transducers rely on the movement of one electrode of a polarized capacitor, thus causing a voltage across the capacitor with a resulting current flow to the load. In piezoelectric transducers, the voltage is generated by deformation of a piezoelectric capacitor. Electromagnetic transducers, instead, consists in the relative motion of a magnetic mass with respect to a coil. The resulting changing in the magnetic flux generates an ac voltage across the coil.

Vibration harvesting has been widely used nowadays. In particular, bi-stable and even tri-stable oscillators allow to scavenge energy from broadband, weak, random vibrations, thus overcoming the lower efficiency of traditional linear resonators (see Fig. 1.6) [5].

Unfortunately, this approach obviously needs particular environmental conditions or specific applications such as automotive, sport-related, etc.

Fig. 1.6. Experimental prototype of tri-stable magnetically-coupled cantilevers having piezoceramic elements as active materials [5].

#### 1.2.2 Thermal harvesting

Thermal harvesters are based on the *Seebeck effect*. This phenomenon produces a voltage difference between two dissimilar electrical conductors or semiconductors kept at different temperatures.

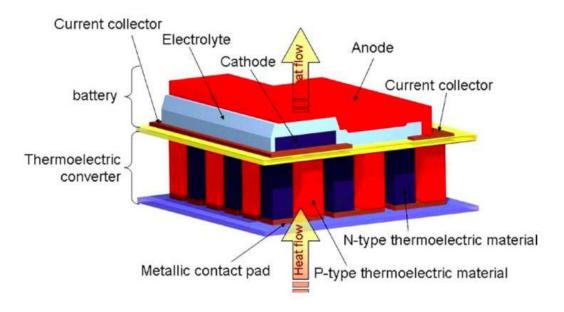

Thermoelectric scavengers were the first ones to appear on the market, since it is easy to fabricate these devices with solid-state technology. A thermoelectric microsystem is shown in Fig. 1.7, whose junctions at the bottom are heated to produce an electrical power current through the Seebeck effect. A large number of junctions can be connected in series to increase the operating voltage.

Fig. 1.7. Artwork of a thermoelectric microsystem [6].

Thermal approach is not widely used within harvesting applications, since it relies on the presence of heat sources.

#### 1.2.3 Photovoltaic harvesting

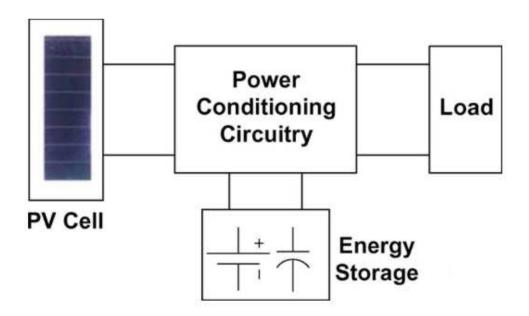

Photovoltaic harvesting systems rely on *photovoltaic* (PV) *cells*, which convert incoming photons into electricity. Recent efforts move on improving PV cell design within indoor application, thus facing the different spectral composition of the light and the lower level of illumination (10-100  $\mu$ W/cm<sup>2</sup>).

A generic photovoltaic harvesting system is shown in Fig. 1.8. The power conditioning circuitry plays an important role within this system. In fact, it draws dc current from the PC cell and efficiently manages both energy storage and power delivering to the load [7].

Fig. 1.8. Scheme of a generic photovoltaic harvesting system [7].

Outdoor photovoltaic harvesting is strongly affected by environmental and time conditions. On the other hand, indoor PV systems overcome the problem related to the environmental conditions but suffer from low efficiency and an artificial light source is also needed.

#### 1.2.4 Radio-frequency harvesting

RF harvesting takes advantage of the incoming electromagnetic radiation from ambient or dedicated sources. Ambient sources relate to public

telecommunication services, such as GSM, WLAN, Wi-Fi, TV and military broadcasting [9]. That means having a constantly available power source, which makes RF harvesting systems widely used nowadays. Dedicated RF sources have been also exploited, e.g. RFID systems, but their power levels have to be set according to international regulations. In fact, although no licenses are needed from the telecommunication regulatory authorities, strict regulations regard the choice of operating frequencies, output powers, spurious emissions, etc.

Table 1.1. Frequency band restrictions for RFID applications.

|    | Frequency<br>Band  | Power                    | Duty<br>Cycle /<br>Tx type       | Channel<br>Spacing /<br>BW | Region              |

|----|--------------------|--------------------------|----------------------------------|----------------------------|---------------------|

| a  | 2446-2454<br>MHz   | 500mW<br>EIRP<br>4W EIRP | Up to 100% ≤ 15%                 | No<br>spacing              | Europe <sup>a</sup> |

| b1 | 865.0-865.6<br>MHz | 100mW<br>ERP             |                                  | 200kHz                     | Europe              |

| b2 | 865.6-867.6<br>MHz | 2W<br>ERP                |                                  | 200kHz                     | Europe              |

| b3 | 867.6-868.0<br>MHz | 500mW<br>ERP             |                                  | 200kHz                     | Europe              |

|    | 902-928<br>MHz     | 4W<br>EIRP               | FH (≥50<br>channels)<br>or DSSS  |                            | USA<br>Canada       |

|    | 2400-2483.5<br>MHz | 4W<br>EIRP               | FH ((≥75<br>channels)<br>or DSSS |                            | USA<br>Canada       |

|    | 2400-2483.5<br>MHz | 10mW<br>EIRP             |                                  | 1MHz<br>BW                 | Japan<br>Korea      |

EIRP stands for Effective Isotropic Radiated Power and is the transmit power multiplied by the gain of the transmit antenna. ERP is Effective Radiated Power. EIRP is 1.64 times ERP. FH stands for Frequency Hopping. DSSS stands for Direct Sequence Spread Spectrum and BW indicates Band Width.

The *industrial, scientific and medical* (ISM) *bands*, have been defined by the *International Telecommunication Union Radiocommunication Sector* (ITU-R), in order to develop standards for radio-communication systems [11]. Frequency bands regulations for RFIDs are shown in Table 1.1 [12].

<sup>&</sup>lt;sup>a</sup> Power levels above 500mW are restricted to use inside the boundaries of a building and the duty cycle of all transmissions shall in this case be  $\leq$  15% in any 200ms period (30ms on / 170ms off).

#### 1.3 RF harvesting systems

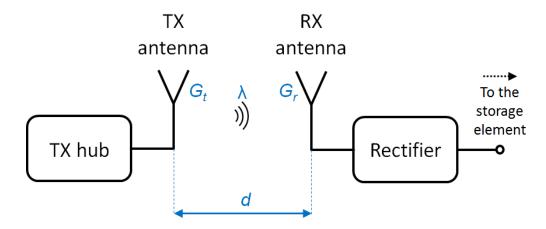

Fig. 1.9. Power propagation scheme between wireless sensor nodes.

A transmitting-receiving pair is shown in Fig. 1.9. By increasing the distance d between nodes, the output power  $P_t$  to the transmitting antenna suffers from higher power losses. This results in a lower power  $P_{AV}$  available at the output terminals of the receiving antenna, as given by the *Friis equation* [13]

$$P_{AV} = P_t G_t G_r \left(\frac{\lambda}{4\pi}\right)^2 \frac{1}{d^n} \tag{1.1}$$

where  $G_t$  and  $G_r$  are the gains of the transmitting and receiving antenna, respectively,  $\lambda$  is the wavelength of the transmitting signal and n is the path loss exponent. The latter goes from 1.6 to 3.3 depending on the propagation channel condition. In particular, n is equal to 2 when the nodes are ideally set into the vacuum.

#### 1.3.1 Rectifier

Once an electric signal is available at the output terminals of the receiving antenna, a circuit is needed to perform the following functions:

- rectifying the ac signal to dc power

- boosting the dc output voltage to a level required by the application

The latter can be simply obtained by exploiting multi-stage implementations of typical RF envelop detectors, as happens for charge pump circuits used within VLSI design. However, transistor threshold voltage  $V_t$  becomes comparable to the rectifier input voltage within low-power applications, thus resulting in lowering the rectifier efficiency.

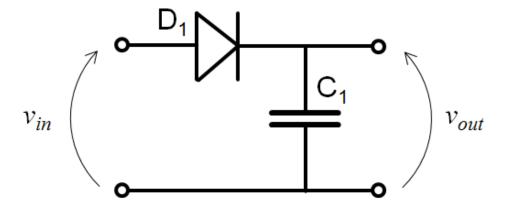

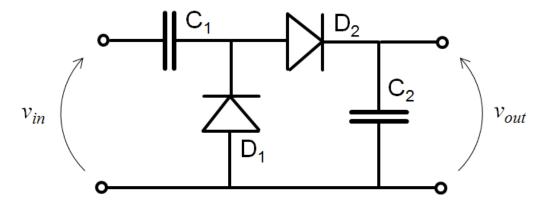

The simplest RF rectifier is the half-wave one, which is shown in Fig. 1.10. During the positive half wave of the input signal  $v_{in}$ , diode  $D_1$  conducts, thus producing a positive voltage across the capacitor  $C_1$ . On the other hand, during the negative half wave of  $v_{in}$ , no current flows through diode  $D_1$ , and the charge into  $C_1$  is delivered to the load. This results in producing a dc voltage  $V_{out}$  across  $C_1$ .

Fig. 1.10. Schematic of the half-wave rectifier.

Fig. 1.11. Schematic of the full-wave rectifier.

Since the circuit in Fig. 1.10 only performs a half-wave rectification, the full-wave counterpart is generally preferred. By referring to Fig. 1.11, the additional two elements  $D_2$  and  $C_2$  provide a full-wave rectification, thus resulting in a more efficient power delivering.

Fig. 1.12. Schematic of the Graetz Bridge.

Another improvement can be achieved by using the *Graetz Bridge* in Fig. 1.12. In fact, this circuit is able to deliver 2-times the output voltage of the previous rectifiers.

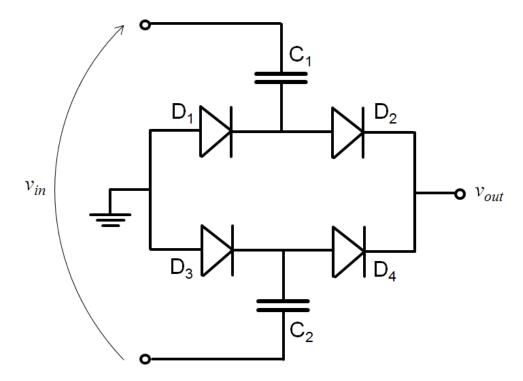

Diode connected transistors were introduced to substitute diodes in the rectifying circuits previously exposed. A MNOS arrangement of the full-wave rectifier is known as Dickson charge pump [14]. The CMOS counterpart based on the Dickson topology is shown, instead, in Fig. 1.13.

Fig. 1.13. Schematic of a Dickson multi-stage rectifier [15].

Although it has been widely used in the last decades, Dickson-based topologies generally exhibit lower power conversion efficiency due to the voltage drop across the rectifying transistors that must exceeds the threshold voltage,  $V_t$ . To this purpose, several compensation techniques have been developed [15]-[17]. In particular, in [15] each transistor gate is connected to proper nodes along the rectifying chain to compensate the threshold voltage drop, thus enhancing the efficiency.

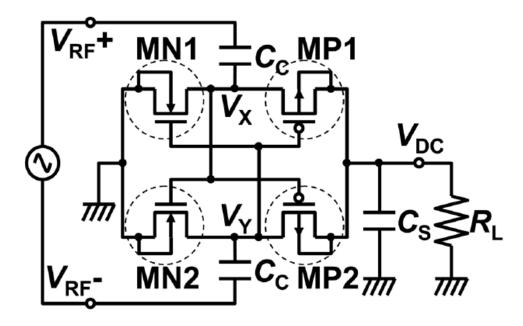

On the other hand, CMOS differential-drive rectifier has been also proposed in the last decade for RF harvester implementations, since an inherent threshold-voltage compensation structure is performed by its cross-coupled connection structure. It consists in a CMOS arrangement based on the Graetz Bridge, as shown in Fig. 1.15.

Fig. 1.14. Schematic of the Dickson-based self compensation topology proposed in [15].

Fig. 1.15. Schematic of the CMOS differential-drive rectifier [18].

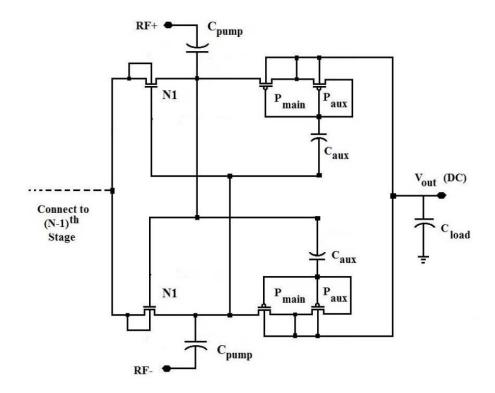

However, it suffers from a reverse conduction that affects both efficiency and sensitivity. Thus, several compensation strategies have been proposed to further improve performance of the differential-drive rectifier. In [19], an additional PMOS transistor was added to each main PMOS transistor to enhance the DC extraction capability, as shown in Fig. 1.16.

Fig. 1.16. Schematic of the CMOS differential-drive rectifier with auxiliary PMOS [19].

An auxiliary stage was used in [20], instead, to properly shift the gate voltage waveform of the basic cell. However, these solutions rely on additional active components, thus resulting effective only for relatively high input power levels. In [21], zero threshold-voltage transistors were used in a complementary CMOS differential-drive rectifier to enhance the efficiency, but silicon-on-sapphire (SOS) CMOS technology was used.

#### 1.3.2 Antenna

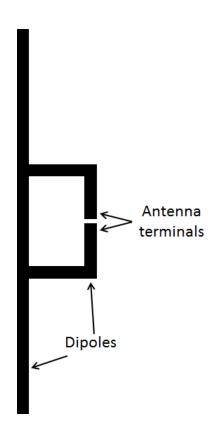

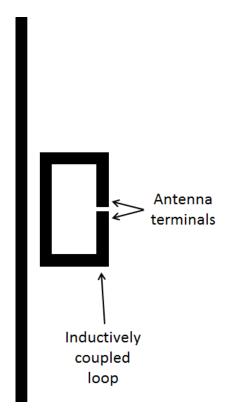

Most of planar antennas for UHF tags are commonly designed as modified dipoles and printed on PCB substrates. Two main categories have been exploited in the last decades: T-match and inductively coupled loop (ICL) antennas [22].

T-match antennas consists in two dipoles connected together, as shown in Fig. 1.17 [23]. Although this is a highly efficient antenna, high values of input resistance are generally found, thus resulting inadequate for matching high-impedance-phase-angle chips, i.e. chips with high parallel input resistance and low capacitance.

Fig. 1.17. Layout of a generic T-match antenna.

Fig. 1.18. Layout of a generic inductively couple loop (ICL) antenna.

ICL antenna, whose layout is shown in Fig. 1.18, is usually preferred due to its inductive coupling that allows a high equivalent inductance to be performed, while maintaining a low series resistance [24]. This feature is very suitable for impedance matching with typical integrated RF rectifiers for harvesting systems.

#### 1.3.3 Design constraints

Although RF harvesting systems have become very popular in the last years, its denomination is not always correctly defined. Indeed, the antenna is often seen as an appendix within the design flow, although the harvesting function is performed by antenna and rectifier working together. Of course, the rectifier is

predominant in terms of design complexity, but accounting for the interaction between antenna and rectifier is mandatory for achieving the best performance of the overall harvesting system.

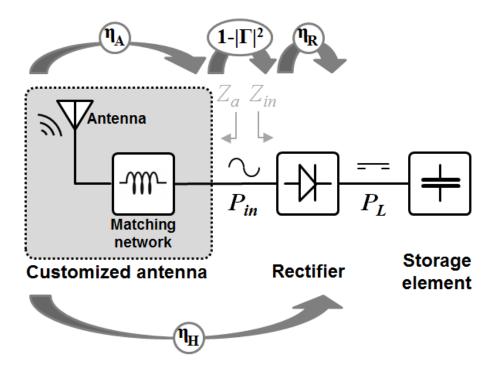

Fig. 1.19. Simplified representation of an RF harvesting system.

Fig. 1.19 shows a simplified block diagram of a generic RF harvesting system. The electromagnetic incident power is converted by the antenna in electric ac power  $P_{in}$  and made available to the rectifier input terminals. The rectifier converts the ac power into a dc power  $P_L$  and delivers it to the storage element, which can be a rechargeable battery or a capacitor. To minimize power losses, a customized antenna is preferred, which inherently performs impedance matching with the rectifier input impedance. The efficiency of the overall harvesting system  $\eta_H$  is defined as

$$\eta_H = P_L / P_{AV} \tag{1.2}$$

where  $P_{AV}$  is the available power assuming an ideally lossless and matched antenna. By considering non-ideal antenna and matching condition, input power  $P_{in}$  is given by

$$P_{in} = \eta_A \left( 1 - \left| \Gamma \right|^2 \right) P_{AV} \tag{1.3}$$

where  $\eta_A$  is the antenna efficiency and  $\Gamma$  is the reflection coefficient at the rectifier/antenna interface. Substituting (1.3) in (1.2) and defining the rectifier efficiency,  $\eta_R$ , as

$$\eta_R = P_L/P_{in} \tag{1.4}$$

the overall system efficiency becomes

$$\eta_H = \eta_A \left( 1 - \left| \Gamma \right|^2 \right) \eta_R \tag{1.5}$$

Since  $P_L$  is imposed by the application, a higher  $\eta_H$  translates into a lower requirement of  $P_{av}$ , which means better sensitivity.

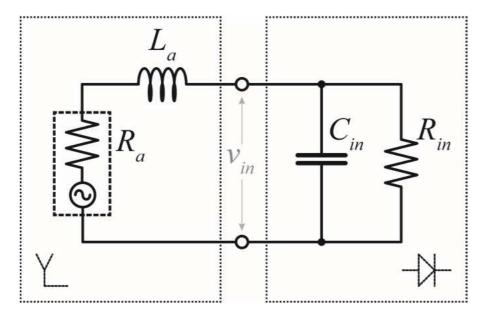

A simplified impedance representation at the antenna and rectifier interface is shown in Fig. 1.20. The antenna is modelled as a first-order network, where resistance  $R_a$  and inductance  $L_a$  account for radiation/loss and reactance, respectively. The rectifier is instead represented by parallel resistance  $R_{in}$  and capacitance  $C_{in}$ . This model is valid for a narrow band approximation of typical ultra-high-frequency (UHF) applications around the operating frequency.

Fig. 1.20. Simplified impedance model of a RF harvesting system.

The input power,  $P_{in}$ , can be expressed as

$$P_{in} = \frac{V_{in}^{2}}{2R_{in}} \tag{1.6}$$

where  $V_{in}$  is the voltage amplitude at the rectifier input terminals. Since the rectifier has a power-up threshold voltage,  $V_{in}$  cannot be lowered at will. Once the minimum  $V_{in}$  is set, a better sensitivity can be achieved by increasing  $R_{in}$ .

On the other hand, the application bandwidth B imposes an additional constraint on the rectifier input impedance through the quality factor,  $Q_L$ , which is given by

$$Q_L = 2\pi f_0 R_{in} C_{in} \tag{1.7}$$

where  $f_0$  is the operating frequency. To this purpose, the Bode-Fano theory defines a maximum allowable value,  $Q_{L,max}$ , for the quality factor that is [7]

$$Q_{L,\max} = \frac{f_0}{B} \frac{2}{\sqrt{1/|\Gamma|^2 - 1}}$$

(1.8)

As far as the antenna is concerned, the constraint on the maximum substrate area greatly limits equivalent inductance  $L_a$  that has to match the rectifier input capacitance. Fortunately, several antenna design techniques can be exploited to reduce the antenna size, while providing the required input reactance.

All the previous aspects need an accurate design strategy, which is capable of efficiently meeting the specifications of the overall harvesting system.

## References

- [1] I. Akyildiz, W. Su, Y. Sankarasubramaniam and E. Cayirci, "Wireless sensor networks: a survey", *Computer Networks*, vol. 38, no. 4, pp. 393-422, 2002.

- [2] G. Papotto, F. Carrara, A. Finocchiaro and G. Palmisano, "A 90-nm CMOS 5-Mbps Crystal-Less RF-Powered Transceiver for Wireless Sensor Network Nodes," in *IEEE Journal of Solid-State Circuits*, vol. 49, no. 2, pp. 335-346, Feb. 2014.

- [3] K. Finkenzeller, "RFID handbook: fundamental and application in contactless smart card and identification", John Wiley and sons, 2003.

- [4] M. Del Prete, A. Costanzo, A. Georgiadis, A. Collado, D. Masotti and Z. Popović, "A 2.45-GHz Energy-Autonomous Wireless Power Relay Node," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 63, no. 12, pp. 4511-4520, Dec. 2015.

- [5] C. Trigona, F. Maiorca, B. Andò and S. Baglio, "Tri-stable behavior in mechanical oscillators to improve the performance of vibration energy harvesters," 2013 Transducers & Eurosensors XXVII: The 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XXVII), pp. 458-461, Barcelona, 2013.

- [6] J. P. Carmo, L. M. Goncalves and J. H. Correia, "Thermoelectric Microconverter for Energy Harvesting Systems," in *IEEE Transactions on Industrial Electronics*, vol. 57, no. 3, pp. 861-867, March 2010.

- [7] A. Nasiri, S. A. Zabalawi and G. Mandic, "Indoor Power Harvesting Using Photovoltaic Cells for Low-Power Applications," in *IEEE Transactions on Industrial Electronics*, vol. 56, no. 11, pp. 4502-4509, Nov. 2009.

- [8] S. Mandal and R. Sarpeshkar, "Low-Power CMOS Rectifier Design for RFID Applications," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.54, no.6, pp.1177,1188, June 2007.

- [9] Intel Corp. Intel ambient RF energy harvesting demonstration. [Online]. Available: <a href="http://www.rfwirelesssensors.com/2009/01/intel-ambientrf-energy-harvesting-demonstration/">http://www.rfwirelesssensors.com/2009/01/intel-ambientrf-energy-harvesting-demonstration/</a>.

- [10] Impinj Inc. SPEEDWAY IPJ-R1000 Reader/Interrogator. [Online]. Available: <a href="http://www.impinj.com/">http://www.impinj.com/</a>.

- [11] ITU-R Radio Regulations, Volume 1, [Online]. Available: <a href="http://www.itu.int">http://www.itu.int</a>.

- [12] H. Visser and R. Vullers, "RF energy harvesting and transport for wireless sensor network applications: principles and requirements", *Proc. IEEE*, vol. 101, no. 6, pp. 1410-1423, June 2013.

- [13] H. J. Visser, Array and Phased Array Antenna Basics. Chichester, U.K.: Wiley, 2005.

- [14] J.F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," *Solid-State Circuits, IEEE Journal of*, vol.11, no.3, pp.374,378, Jun 1976.

- [15] G. Papotto, F. Carrara, and G. Palmisano, "A 90-nm CMOS Threshold-Compensated RF Energy Harvester," *Solid-State Circuits, IEEE Journal of*, vol.46, no.9, pp.1985,1997, Sept. 2011.

- [16] Hameed, Z.; Moez, K., "A 3.2 V –15 dBm Adaptive Threshold-Voltage Compensated RF Energy Harvester in 130 nm CMOS," in *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.62, no.4, pp.948-956, April 2015.

- [17] J. Shin, I.-Y. Chung, Y. J. Park, and H. S. Min, "A new charge pump without degradation in threshold voltage due to body effect [memory applications]," in *Solid-State Circuits, IEEE Journal of*, vol.35, no.8, pp.1227-1230, Aug. 2000.

- [18] K. Kotani, A. Sasaki, and T. Ito, "High-Efficiency Differential-Drive CMOS Rectifier for UHF RFIDs," *Solid-State Circuits, IEEE Journal of*, vol.44, no.11, pp.3011,3018, Nov. 2009.

- [19] S.S. Chouhan and K. Halonen, "A modified cross coupled rectifier based charge pump for energy harvesting using RF to DC conversion," *Circuit Theory and Design (ECCTD)*, 2013 European Conference on , pp.1,4, 8-12 Sept. 2013.

- [20] P. Kamalinejad, K. Keikhosravy, R. Molavi, S. Mirabbasi, and V.C.M. Leung, "Efficiency enhancement techniques and a dual-band approach in RF rectifiers for wireless power harvesting," in *Circuits and Systems (ISCAS)*, 2014 IEEE International Symposium on , pp.2049-2052, 1-5 June 2014.

- [21] P.T. Theilmann, C.D. Presti, D.J. Kelly, and P.M. Asbeck, "A μW Complementary Bridge Rectifier With Near Zero Turn-on Voltage in SOS CMOS for Wireless Power Supplies," in *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.59, no.9, pp.2111-2124, Sept. 2012.

- [22] G. Marrocco, "The art of UHF RFID antenna design: impedance-matching and size-reduction techniques," *IEEE Antennas and Propagation Mag.*, vol. 50, no. 1, pp. 66-79, Feb. 2008.

- [23] C. A. Balanis, Antenna Theory, Analysis and Design, Second Edition, New York, John Wiley & Sons Inc., 1997.

- [24] H. W. Son and C. S. Tyo, "Design of RFID Tag Antennas Using an Inductively Coupled Feed," *Electronics Letters*, 41, 18, September 2005, pp. 994-996.

# **Chapter II**

## **CMOS** differential-drive rectifier

## 2.1 Operating principle

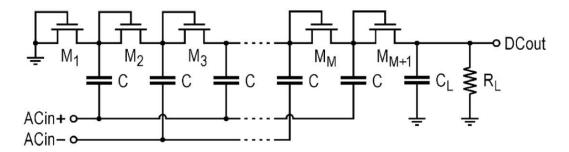

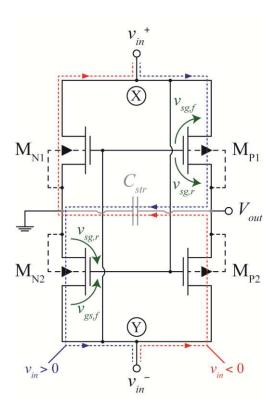

The operating principle of the single-stage CMOS differential-drive rectifier in Fig. 2.1 can be explained as follows [1]. Assuming a sinusoidal input signal

$$v_{in}(t) = v_{in}^{(+)}(t) - v_{in}^{(-)}(t) = V_{in}\sin(\omega t)$$

(2.1)

if  $v_{in}$  is positive (negative),  $M_{P1}$  and  $M_{N2}$  are on (off) and  $M_{P2}$  and  $M_{N1}$  are off (on). Therefore, a positive output current is generated in the storage capacitor,  $C_{str}$ , regardless the sign of  $v_{in}$ , thus producing a dc output voltage,  $V_{out}$ .

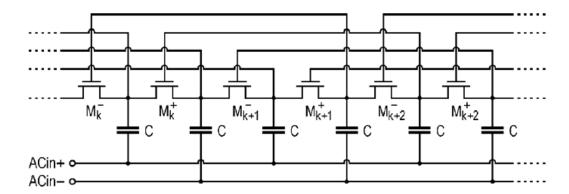

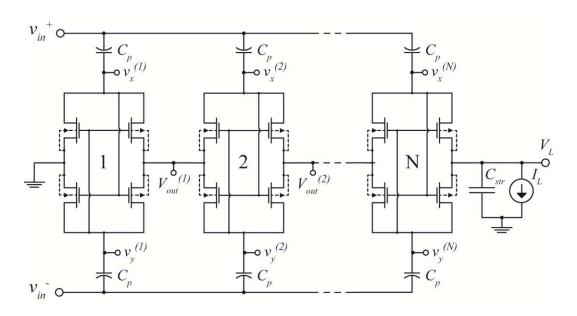

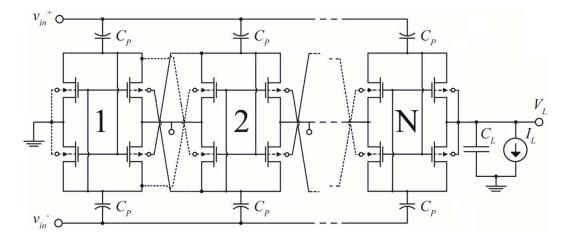

RF rectifiers for energy harvesting are typically designed to supply an output voltage,  $V_L$ , to the load, which is higher than the RF input amplitude. To achieve high values of  $V_L$ , a multi-stage rectifier is used as shown in Fig. 2.2, where N stages are coupled to the RF input signal through the pump capacitors,  $C_p$  [2]-[3].

Fig. 2.1. Schematic of the single-stage CMOS differential-drive.

Fig. 2.2. Schematic of the multi-stage CMOS differential-drive.

In this way

$$V_{out}^{(n)} \approx nV_{out}^{(1)} ; n = 1, 2, ..., N$$

(2.2)

where

$$V_{out}^{(1)} = V_{out} = \alpha V_{in} - V_{on}$$

(2.3)

is the dc output voltage contribution of a single stage, being  $\alpha V_{in}$  the amplitude of the transistor drive voltage and  $V_{on}$  the voltage drop across the couple of on-state transistors, i.e.  $M_{P1}/M_{N2}$  or  $M_{P2}/M_{N1}$  depending on the sign of  $v_{in}$ . Coefficient  $\alpha$  accounts for the capacitive partition between  $C_p$  and the parasitic capacitance  $C_{par}$  between nodes X and Y in Fig. 2.1 mainly due to the transistor size. By using (2.2) and (2.3), it results

$$V_{out}^{(N)} = V_L = N(\alpha V_{in} - V_{on})$$

(2.4)

Equation (2.4) is valid under the assumption of symmetric stages, which means to isolate n-type transistor bulk by adopting a triple-well technology.

For the generic  $n^{th}$ -stage, the steady state behavior at nodes X and Y is approximately expressed by

$$v_x^{(n)}(t) = \left(n - \frac{1}{2}\right) V_{out} + \frac{1}{2} \alpha v_{in}(t)$$

(2.5)

$$v_{y}^{(n)}(t) = \left(n - \frac{1}{2}\right) V_{out} - \frac{1}{2} \alpha v_{in}(t)$$

(2.6)

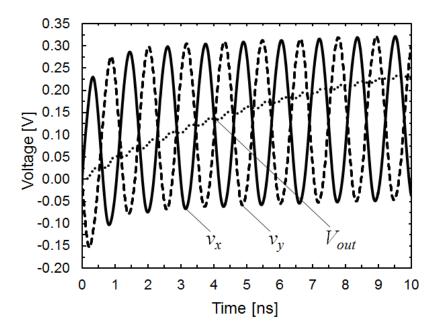

The dc component in (2.5) and (2.6) can easily be explained by considering that nodes X and Y are alternatively connected to  $V_{out}^{(n)}$  and  $V_{out}^{(n-1)}$ , thus resulting in a square wave at the same frequency of  $v_{in}$  and with an average value of  $(n-1/2)V_{out}$ . Considering an 868-MHz input signal with a 0.4-V amplitude, typical transient waveforms for  $v_x$ ,  $v_y$  and  $V_{out}$  in the first stage are shown in Fig. 2.3.

Fig. 2.3. Typical voltage waveforms in internal nodes, X and Y, of the first stage of a CMOS differential-drive rectifier.

By inspecting the basic cell in Fig. 2.1, a slightly positive  $v_{in}$  is not enough to charge  $C_{str}$ . Indeed, considering e.g. transistors  $M_{P1}$  and  $M_{N2}$ , a forward current charging  $C_{str}$  is produced only when  $v_{sg,f} > v_{sg,r}$  and  $v_{gs,f} > v_{gs,r}$  in  $M_{P1}$  and  $M_{N2}$ ,

respectively. Using (2.4-2.6), that include the effect of the pump capacitors, these conditions on gate-source voltages lead to

$$\alpha V_{in}(t) > V_{out} \tag{2.7}$$

On the other hand, a reverse current appears discharging the storage capacitor when  $\alpha v_{in}(t) < V_{out}$ , which is a typical loss mechanism of the full-wave rectifier affecting its efficiency.

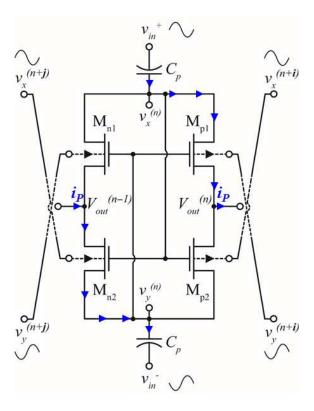

## 2.2 Proposed topology

The proposed approach lies in the threshold-voltage variation techniques based on body-voltage control. Specifically, it reduces or increases  $V_t$  depending on whether the transistor in the rectifying stage is pushed in forward or reverse conduction, respectively. The improvement is achieved by properly driving the transistor bulk terminals with control signals inherently available in the original rectifier [4].

Fig. 2.4 shows the proposed approach, where only the generic  $n^{th}$ -stage of the rectifier is considered for simplicity. In the following, it is demonstrated that internal signals,  $v_x$  and  $v_y$ , in (2.5) and (2.6), can well be exploited as control signals since they provide a tunable dc component and a complementary variable component that are suitable to drive the bulk terminals. Specifically, the optimum dc component,  $V_{opt,p}$  ( $V_{opt,n}$ ), is the same for the two p-type (n-type) transistors of the  $n^{th}$ -stage and can be fulfilled by selecting the proper n-i (n-j) stage from which signals  $v_x$  and  $v_y$  are derived.

Fig. 2.4. Schematic of the generic  $n^{th}$ -stage with the proposed improvement.

The optimum index i (j) is valid for all the stages of the entire multi-stage rectifier, except for those stages in which the condition  $1 \le n$ —index  $\le N$  is not satisfied. For these stages, the bulks of p-type and n-type transistors can be connected to  $V_L$  and ground, respectively.

Let us now evaluate the bulk-source voltages of the transistors for the  $n^{th}$ -stage. By referring to the transistor  $M_{P1}$ , the resulting expression for  $v_{bs,P1}^{(n)}$  depends on the input signal. Indeed, the source voltage  $v_{s,P1}^{(n)}$  is equal to  $V_{OUT}^{(n)}$  when  $M_{P1}$  works in reverse conduction and coincides with  $v_x^{(n)}(t)$  in forward conduction. Therefore, using (2.3-2.6), the proposed solution leads to

$$v_{bs,P1}^{(n)}(t) = \begin{cases} (i - 1/2)V_{out} - \alpha v_{in}(t)/2 & \alpha v_{in}(t) < V_{out} \\ iV_{out} - \alpha v_{in}(t) & \alpha v_{in}(t) \ge V_{out} \end{cases}$$

(2.8)

whereas in the classic differential-drive rectifier

$$v_{bs,P1}^{(n)}(t) = \begin{cases} 0 & \alpha v_{in}(t) < V_{out} \\ V_{out}/2 - \alpha v_{in}(t)/2 & \alpha v_{in}(t) \ge V_{out} \end{cases}$$

(2.9)

During the overall conduction angle of the input signal,  $v_{bs,Pl}^{(n)}$  varies in a range given by

$$\Delta v_{bs,Pl}^{(n)}(t) = v_{bs,Pl}^{(n)}(t) \big|_{v_m = -V_m} - v_{bs,Pl}^{(n)}(t) \big|_{v_m = V_m}$$

(2.10)

where  $V_{in}$  is the input amplitude according to (2.1). Using in (2.10) the values of  $v_{bs,Pl}^{(n)}$  in (2.8) for forward and reverse conduction, the proposed solution provides a maximum bulk-source variation equal to

$$\Delta v_{bs,P1}^{(n)}(t) = (3\alpha V_{in} - V_{out})/2 \tag{2.11}$$

that is much higher than

$$\Delta v_{bs,P1}^{(n)}(t) = (\alpha V_{in} - V_{out})/2$$

(2.12)

derived from (2.9) and (2.10) for the classic solution. This results in a higher variation of  $V_t$  for the proposed rectifier, according to the body-effect equation.

Index i (j) can easily be found with simulations by properly applying signal  $\alpha v_{in}(t)/2$  to the bulk terminals of the  $n^{th}$ -stage and sweeping its dc component to

maximize efficiency. Due to the modularity of the rectifier, index i (j) derived for the generic n<sup>th</sup>-stage will be valid for all the rectifier stages and hence further simulations are not required. By equating the optimum dc component derived from simulation,  $V_{opt,p}$ <sup>(n)</sup>, to the dc component in (2.4), we can find index i as

$$i = \left[ \frac{V_{opt,p}^{(n)}}{V_{out}} + \frac{1}{2} - n \right]$$

(2.13)

where

$$V_{opt,p}^{(n)} = V_{opt,p}^{(1)} + (n-1)V_{out}$$

(2.14)

being  $V_{opt,p}^{(1)}$  referred to the rectifier ground and remembering that  $V_{OUT}^{(n-1)}$  is  $(n-1)V_{OUT}$ , according to (2.2). Index j can be derived in the same way by substituting  $V_{OPT,p}^{(n)}$  with  $V_{OPT,p}^{(n)}$  in (2.13).

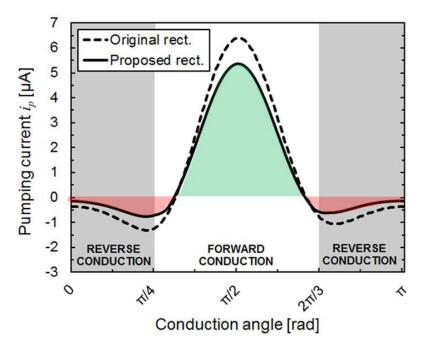

Fig. 2.5 shows the shape of the steady-state pumping current,  $i_P$ , for the compensated  $n^{th}$ -stage in Fig. 2.4 during the positive half-wave of the input signal. In this simulation, the single-stage dc voltage contribution,  $V_{out}$ , and the average output current were set to 240 mV and 1  $\mu$ A, respectively. Current  $i_P$  flows in  $M_{P1}$  and  $M_{N2}$  (thanks to the stage symmetry) and goes to the output terminals  $V_{out}^{(n)}$  and  $V_{out}^{(n-1)}$ . Fig. 2.4 also shows the same current under equal output conditions for the uncompensated stage, i.e. with the bulk terminals connected as in Fig. 2.1. The current in the white area flows in the positive direction and hence will be transferred to next stages and finally delivered to the storage capacitor at the multi-stage rectifier output. The grey areas in Fig. 2.5 show instead the reverse

conduction windows where current  $i_P$  is negative and hence discharges the storage capacitor. Similar current waveforms are produced with the negative half-wave of the input signal thanks to  $M_{N1}$  and  $M_{P2}$ . Thanks to the reduced reverse current, a lower forward current is needed in the compensated stage to satisfy the same output conditions. This means lower power consumption and hence better efficiency and input sensitivity.

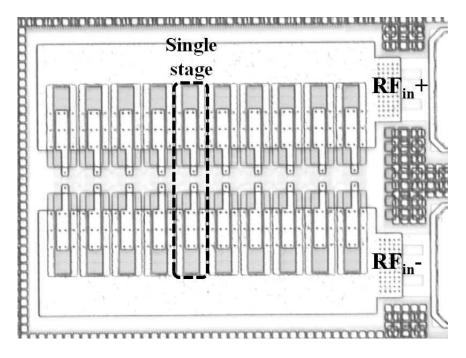

An example with i = -j = 1 is shown in Fig. 2.6, where the n-type transistors of the first stage and the p-type transistors of the last stage were connected to ground and output, respectively.

Fig. 2.5. Steady-state pumping current of the proposed and classic rectifier stage.

Fig. 2.6. Simplified example with i = -j = 1 of the proposed CMOS differential-drive rectifier with body voltage control.

## 2.3 Rectifier model

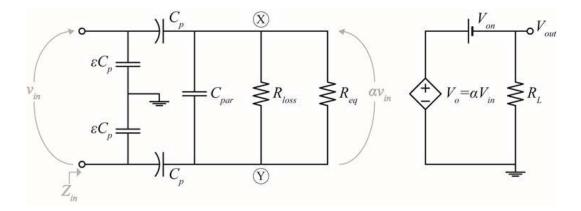

A model for the CMOS differential-drive rectifier is useful to well understand how design parameters are linked to specifications. Fig. 2.7 shows a linear model of a single-stage rectifier based on a voltage-controlled voltage source [1], where  $C_p$  and  $C_{par}$  have been already defined in previous section,  $R_{eq}$  is the equivalent resistance of the ideally lossless rectifier,  $R_{loss}$  accounts for losses mainly due to reverse current, and  $\varepsilon C_p$  is the parasitic capacitance between the bottom plate of  $C_p$  and ground.

$R_{eq}$  can be evaluated by equating the input ac power with the load power as follows

$$\frac{(\alpha V_{in})^2}{2R_{eq}} = \frac{V_{out}^2}{R_L}$$

(2.15)

Fig. 2.7. Linear model of a single-stage full-wave rectifier.

where  $\alpha$  is given by

$$\alpha = \frac{C_p}{C_p + 2C_{par}} \tag{2.16}$$

Therefore,  $R_{eq}$  in the ideal rectifier is approximately related to the ratio of  $V_{in}$  to  $V_{out}$  and to the load resistance. By substituting (2.3) in (2.15), an expression of  $R_{eq}$  dependent on  $V_{on}$  is achieved that is given by

$$R_{eq} = \frac{1}{2} \left( \frac{\alpha V_{in}}{\alpha V_{in} - V_{on}} \right)^2 R_L \tag{2.17}$$

By inspection of Fig. 2.7, the input resistance of the single-stage rectifier results

$$R_{in}^{(1)} = \left(R_{eq} \parallel R_{loss}\right) \left(1 + 2\frac{C_{par}}{C_{p}}\right) = \frac{R_{eq} \parallel R_{loss}}{\alpha}$$

(2.18)

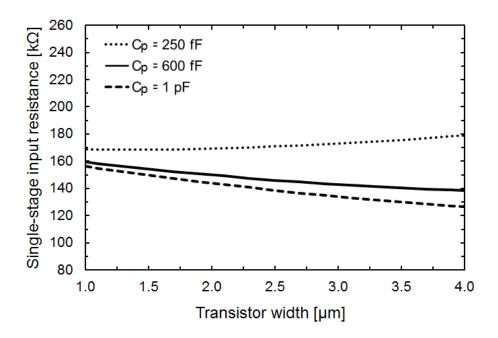

Fig. 2.8 shows  $R_{in}^{(1)}$  as a function of W for three values of  $C_p$ . It is apparent that  $R_{in}^{(1)}$  slightly depends on W and becomes nearly constant for low  $C_p$ .

Fig. 2.8. Simulated input resistance of the single-stage rectifier versus transistor W for different  $C_p$  values.

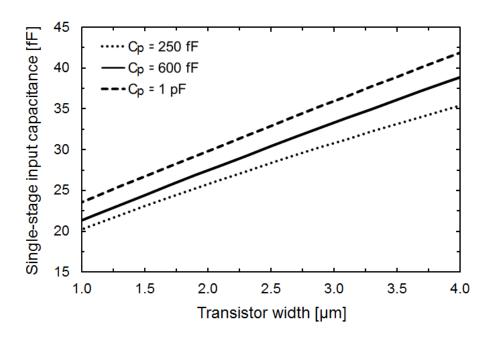

As far as input capacitance  $C_{in}^{(I)}$  is concerned, it can easily be calculated from the model in Fig. 2.7. It results

$$C_{in}^{(1)} = C_p \left( \frac{\varepsilon}{2} + \frac{C_{par}}{C_p + 2C_{par}} \right) = \frac{\varepsilon C_p}{2} + \alpha C_{par}$$

(2.19)

The dependence of  $C_{in}^{(I)}$  on W is shown in Fig. 2.9.  $C_{in}^{(I)}$  linearly depends on W but its dependence on  $C_p$  is low. Indeed, an increase of  $C_p$  by a factor of four (i.e., from 250 fF to 1 pF) increases  $C_{in}^{(I)}$  by only 20%. This means that the input capacitance mainly depends on parasitic capacitances due to rectifying transistors, which are related to W.

Fig. 2.9. Simulated input capacitance of the single-stage rectifier versus transistor W for different  $C_p$  values.

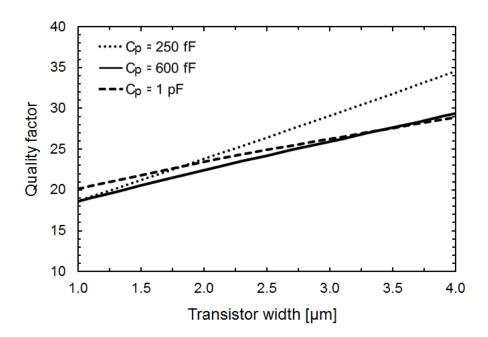

Fig. 2.10. Simulated quality factor of the single-stage rectifier versus transistor W for different  $C_p$  values.

Fig. 2.8 and Fig. 2.9 say that W impacts on  $R_{in}^{(1)}$  much less than on  $C_{in}^{(1)}$ . Therefore, quality factor Q that is determined by the product of  $R_{in}^{(1)}$  with  $C_{in}^{(1)}$  exhibits the same linear dependence on W and the same slight dependence on  $C_p$  than  $C_{in}^{(1)}$ , as shown in Fig. 2.10.

Finally, the rectifying stages are placed in parallel in the multi-stage rectifier and hence the input resistance and capacitance,  $R_{in}$  and  $C_{in}$ , can simply be expressed as

$$R_{in} = \frac{R_{in}^{(1)}}{N} \tag{2.20}$$

$$C_{in} = NC_{in}^{(1)} (2.21)$$

Therefore, Q does not depend on the number of rectifying stages. Of course,  $C_{in}$  should be corrected to account for both the input pad and layout parasitic capacitances. It is suggested to not use pump capacitors  $C_p$  too small to avoid that coefficient  $\alpha$ , and hence the transistor drive voltage, greatly depends on the layout parasitic capacitances.

## References

- [1] A. Facen and A. Boni, "Power Supply Generation in CMOS Passive UHF RFID Tags," *Research in Microelectronics and Electronics 2006, Ph. D.*, pp.33,36, 2006.

- [2] S. Mandal and R. Sarpeshkar, "Low-Power CMOS Rectifier Design for RFID Applications," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.54, no.6, pp.1177,1188, June 2007.

- [3] K. Kotani, A. Sasaki, and T. Ito, "High-Efficiency Differential-Drive CMOS Rectifier for UHF RFIDs," *Solid-State Circuits, IEEE Journal of*, vol.44, no.11, pp. 301, 3018, Nov. 2009.

- [4] L. Grasso, R. Guerra, and G. Palmisano, "A CMOS full-wave rectifer with threshold compensation based on inherent body-voltage control," To be published in *Microwave Conference (EuMC)*, 2016 European, London, 2016.

# **Chapter III**

## Antenna

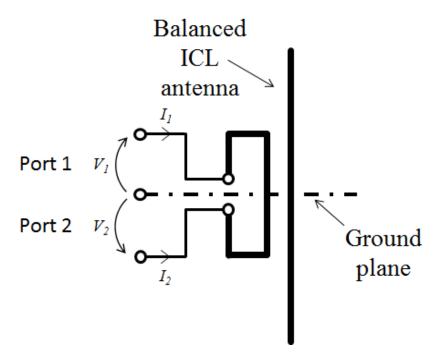

## 3.1 Proposed ICL antenna

An ICL antenna is made up of an inductive small loop, which is closely coupled to a radiating body, as shown in Fig. 3.1. Within the present system design, the substrate area was set to the credit card dimensions as defined by standard ISO/IEC 7810 ID-1, i.e.  $85.6 \times 54$  mm. The two terminals of the loop are connected to the rectifier chip. Operating frequency and substrate permittivity set the length of the radiating body, which was folded to meet the area constraint 0-[2]. The inductive loop has a rectangular shape to enhance inductive coupling that needs length a much grater than width b. The bi-conical shape of the radiating body is generally adopted to increase bandwidth [3], but in this design it was mainly exploited to accurately set the impedance matching. Moreover, a slot was cut out from the radiating body to further enhance inductive coupling.

Fig. 3.1. Layout of the proposed inductively coupled loop antenna.

Loop perimeter p=2(a+b) and distance d from the radiating body are the main design parameters, which determine the antenna output resistance and reactance,  $R_a$  and  $X_a$ ,  $(X_a = \omega L_a)$  and the efficiency,  $\eta_A$ , as shown in Fig. 3.2 and Fig. 3.3, respectively, where also the impedance quality factor, Q, was plotted.

Specifically, Fig. 3.2 shows a family of curves of the antenna series resistance and reactance as function of parameters p and d. As apparent in Fig. 3.2, input reactance depends only on p (i.e., on the loop equivalent inductance), whereas input resistance is due to both inductive coupling and loop resistive losses mainly related to d and p, respectively. On the other hand, increasing d reduces coupling between the loop and the radiating body, thus leading to lower antenna efficiency.

Fig. 3.2. Simulated level curves showing series resistance  $R_a$  and reactance  $X_a$  of the proposed ICL antenna.

Fig. 3.3. Simulated level curves showing efficiency  $\eta_A$  and quality factor Q of the proposed ICL antenna.

Moreover, antenna efficiency reduces as quality factor increases. Indeed, the antenna quality factor Q is

$$Q = \frac{2\pi f_0 L_a}{R_a} \tag{3.1}$$

where  $R_a$  accounts for both radiation and loss resistances but it is usually dominated by the former. Therefore, Q can manly be increased by increasing  $L_a$ , which in turn means higher loss resistances and lower antenna efficiency. Finally, the efficiency degradation in the upper side of Fig. 3.3 is due to a high loop perimeter that reduces the distance of segments b from the radiating body for a given area constrain, thus introducing spurious coupling.

A 3D radiation pattern is shown in Fig. 3.4. The antenna is quite isotropic in the x-z plane, while no power is radiated along y axis.

Fig. 3.4. Radiation pattern of the proposed ICL antenna.

# References

[1] G. Marrocco, "The art of UHF RFID antenna design: impedance-matching and size-reduction techniques," *Antennas and Propagation Magazine, IEEE*, vol.50, no.1, pp.66,79, Feb. 2008.

- [2] Wonkyu Choi, H. W. Son, Chansoo Shin, Ji-Hoon Bae and Gilyoung Choi, "RFID tag antenna with a meandered dipole and inductively coupled feed," 2006 IEEE Antennas and Propagation Society International Symposium, Albuquerque, NM, 2006, pp. 619-622.

- [3] A. A. Eldek, A. Z. Elsherbeni, C. E. Smith and Kai-Fong Lee, "Wideband slot antennas for radar applications," *Radar Conference*, 2003. *Proceedings of the* 2003 IEEE, 2003, pp. 79-84.

# **Chapter IV**

# **Co-design methodology**

#### 4.1 General outline

The proposed co-design procedure provides a system design strategy to maximize the performance of the overall harvesting system once rectifier and antenna are connected together. As a first step, a preliminary design of the rectifier is carried out as starting point before proceeding with the co-design procedure. Then, an antenna matching chart is used, which shows antenna efficiency  $\eta_A$  and quality factor Q for each matching-impedance operating point. Finally, the rectifier is properly re-designed to achieve the best performance of the antenna-rectifier system. Importantly, harvester performance is maximized at sensitivity, since it sets the most important performance parameter of a harvesting system application that is maximum operating distance.

# 4.2 Rectifier design

Co-design procedure requires a lower number of iterations if the optimum stand-alone solution for the rectifier is assumed as starting point. For a given signal bandwidth and load specification, the optimum rectifier design is achieved by setting transistor size W, number of stages N, and pump capacitances  $C_p$ , which maximize efficiency  $\eta_R$ .

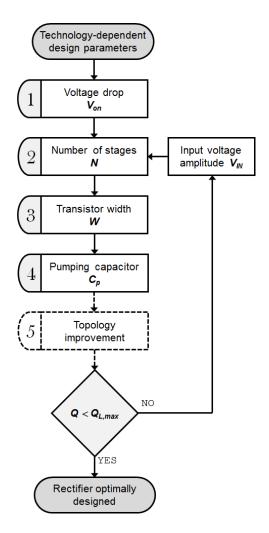

Fig. 4.1. Proposed design flow for the differential-drive rectifier.

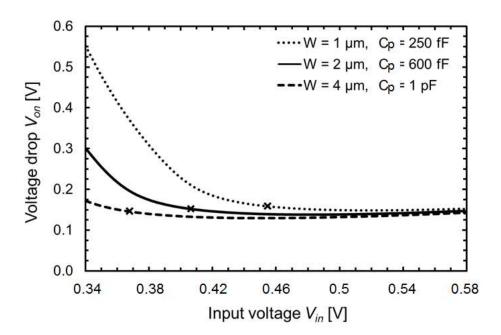

Fig. 4.2. Simulated curves of  $V_{on}$  versus  $V_{in}$  at different couples of width and pump capacitance values for a single-stage CMOS full-wave rectifier ( $V_{out} = 240 \text{ mV}$ ,  $I_L = 1 \text{ }\mu\text{A}$ ).

### 4.2.1 Technology-dependent design parameters

Fig. 4.1 shows the flow chart of the proposed design strategy for a differential-drive rectifier. As design constrain, the ratio of p-type and n-type transistor size is set according to the mobility ratio to guarantee conduction symmetry in both transistors.

#### 4.2.2 Voltage-drop estimation

Step 1 in the design flow in Fig. 4.1 addresses the estimation of voltage  $V_{on}$ , which is required in step 2 to find the number of stages, N, for the optimum stand-alone rectifier. Voltage  $V_{on}$  depends on  $V_{in}$ , W, and  $C_p$ , as shown in Fig. 4.2 for a single-stage rectifier, where it is plotted for three different couples of W and

$C_p$ , at  $I_L$  = 1  $\mu$ m. Fig. 4.2 also shows for each couple of W and  $C_p$  the value of  $V_{in}$  that maximizes efficiency (see crosses). The related values of  $V_{on}$  fall in the knee regions where  $V_{on}$  approaches its asymptotic value, which is the same regardless the values of the design parameters. Therefore,  $V_{on}$  can well be estimated with this asymptotic value by simply increasing  $V_{in}$  at will.

#### 4.2.3 Number of stages

If  $C_p$  is considerable higher than  $C_{par}$ ,  $\alpha$  in (2.16) is close to unity and the transistor drive voltage,  $\alpha v_{in}$ , approaches  $v_{in}$ . It is recommended to work with an input amplitude voltage  $V_{in}$  as low as possible [1] to reduce reverse currents. However, by working with  $V_{in}$  below the threshold voltage, the rectifier output power becomes extremely low. As tradeoff between low reverse current and acceptable output power, input voltage amplitude  $V_{in}$  is set equal to the p-type threshold voltage,  $V_{t,p}$ , being it usually higher than the n-type one. Using (2.4), the number of stages, N, in step 2 is given by

$$N = \frac{V_L}{V_{th,p} - V_{on}} \tag{4.1}$$

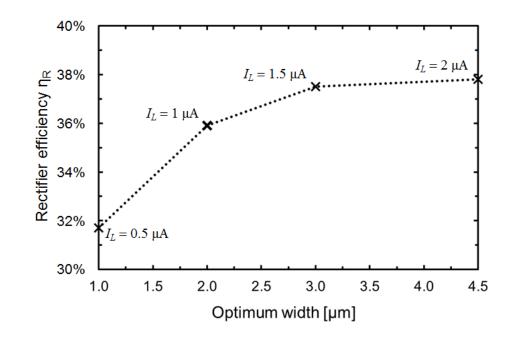

#### 4.2.4 Transistor width

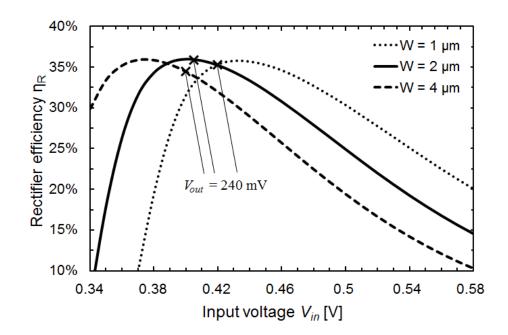

Step 3 in the flow chart concerns transistor size W that is set for optimum rectifier efficiency. To this purpose, Fig. 4.3 shows the designs for an output voltage of 240 mV and four load currents, in which for each current an optimum W for maximum  $\eta_R$  is determined. As apparent in Fig. 4.3, higher load current

leads to higher  $\eta_R$  along with higher W. Fig. 4.4 shows  $\eta_R$  as function of input voltage for different values of W at  $I_L = 1 \mu m$ , where a voltage of 240 mV was considered as output specification. Despite the three curves have the same maximum  $\eta_R$ , only the design with  $W = 2 \mu m$  achieves this maximum, thanks to  $V_{in}$  that is almost equal to the transistor threshold voltage (i.e., 0.4 V).

It is worth noting that the curve with  $W=1~\mu m$  gives the maximum  $\eta_R$  with a slightly higher  $V_{out}$ . However, exceeding the output specification leads to lower sensitivity. On the other hand, the curve with  $W=4~\mu m$  achieves the maximum  $\eta_R$  with  $V_{out}$  and hence does not meet specification.

Fig. 4.3. Rectifier efficiency evaluated at different load currents ( $V_{out} = 240 \text{ mV}$ ).

Fig. 4.4. Simulated curves of  $\eta_R$  versus  $V_{in}$  at different width values for a single-stage CMOS full-wave rectifier ( $V_{out} = 240$  mV,  $I_L = 1 \mu A$ ).

### 4.2.5 Pumping capacitors

Step 4 sets  $C_p$ . In principal, this capacitance can be set to a low value. Indeed, Q only slightly depends on  $C_p$  as discussed in Chapter II (see Fig. 2.10) and the same peak of  $\eta_R$  is still achieved with a low capacitance as shown in Fig. 4.5. However, robustness to layout parasitic capacitances and  $\alpha$  suggests a value of  $C_p$  not too small, as mentioned before. Moreover, a Q with a low  $C_{in}$  and a high  $R_{in}$  results in a worse operating point in terms of  $\eta_A$  for the antenna.

Fig. 4.5. Simulated curves of  $\eta_R$  versus  $V_{in}$  at different pump capacitance values for a single-stage CMOS full-wave rectifier  $(V_L = 240 \text{ mV}, I_L = 1 \text{ } \mu\text{A})$ .

### 4.2.6 Topology improvement

A step 5 is included that accounts for additional design parameters, if a different arrangement with respect to the conventional topology of differential-drive rectifier to improve its performance. In this work, the additional parameters is the index i(j), which defines how the connections between transistor bulks and internal nodes have to be accomplished [2].

### 4.2.7 Maximum allowable quality factor

In the final step, the Q of the rectifier input impedance is compared with the maximum allowable value,  $Q_{L,max}$ , for the bandwidth specification. If the quality

factor is higher than  $Q_{L,max}$ , a W lower than the optimum value defined in step 3 is needed according to Fig. 2.10, unavoidably leading to a lower sensitivity.

Fig. 4.6. Simulated curves of Q versus W at different pump capacitance values for a single-stage CMOS full-wave rectifier  $(V_L = 240 \text{ mV}, I_L = 1 \text{ } \mu\text{A})$ .

## 4.3 Co-design approach

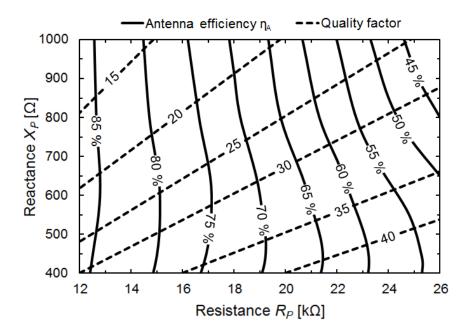

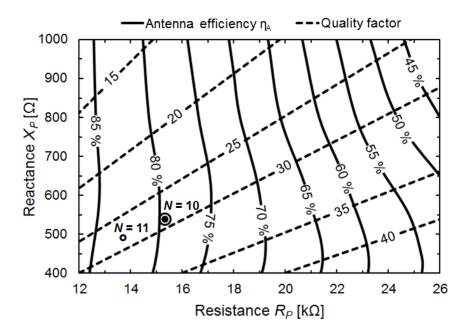

Antenna chart is shown in Fig. 4.7, in which  $\eta_A$  and Q is plotted as a function of parallel input resistance  $R_p$  and reactance  $X_p$ . The matching chart is achieved by combining charts in Fig. 3.2 and Fig. 3.3. The operating point of the antenna/rectifier system identifies a point in the antenna chart. Since antenna and rectifier have to be matched together, each point in the chart in also the complex conjugate of the rectifier input impedance. The operating point provides the expected system efficiency,  $\eta_H$ , as a product of  $\eta_A$  and  $\eta_R$ .

Fig. 4.7. Antenna matching chart adopted in the proposed co-design methodology.

To find the optimum system for the best performance in terms of efficiency, an effective way is to vary the number of stages, N, of the rectifier. Indeed, the variation of N does not affect Q, as can be found by multiplying (2.20) and (2.21), being

$$Q_L = 2\pi f_0 R_{in} C_{in} \tag{4.2}$$

and hence the bandwidth requirement is preserved. Moreover, the variation of N significantly changes the operating point in the antenna chart thus facilitating system performance optimization. Finally, the rectifier input impedance changes in a predictable way as apparent again from (2.20) and (2.21). Unfortunately, this behavior is not exactly true for the proposed rectifier topology due to the asymmetry induced by the body-voltage control. However, the impact of this

asymmetry on the impedance becomes negligible for a number of stages starting from 4. Fortunately, more than 5 stages are usually needed in common applications where output voltages higher than 1 V are required. Therefore, the proposed rectifier well fits with the co-design procedure discussed before.

Three designs were carried out to meet output specifications of typical applications. They are:

(A)

$$V_L = 1.2 \text{ V} \text{ and } I_L = 1.2 \text{ } \mu\text{A};$$

(B)

$$V_L = 2.4 \text{ V} \text{ and } I_L = 600 \text{ nA};$$

(C)

$$V_L = 2.4 \text{ V} \text{ and } I_L = 1 \text{ } \mu\text{A}.$$

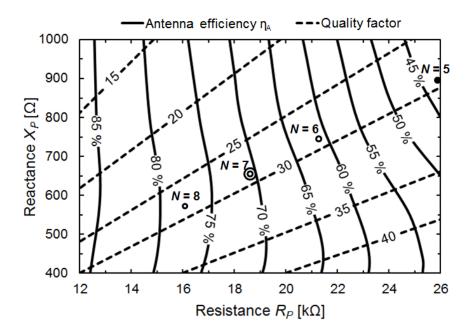

Detailed iteration data of both antenna and rectifier efficiency for the three designs are reported in Table 4.2, Table 4.3 and Table 4.4. By referring to the co-design procedure for design A that is shown in Fig. 4.8, the rectifier starting point (i.e., the optimum stand-alone rectifier) is indicated with a filled circle in the antenna chart, while empty circles refer to the iterations. Instead, the concentric circle is the optimum harvesting system design (i.e., with maximum  $\eta_H$ ). A handful legend regarding the iteration circles is shown in Table 4.1.

Table 4.1. Legend of the iteration circles shown in Fig. 4.8, Fig. 4.9, and Fig. 4.10.

|         | opt. $\eta_R$ | opt. $\eta_H$ |  |

|---------|---------------|---------------|--|

| 0       | NO            | NO            |  |

| •       | YES           | NO            |  |

| 0       | NO            | YES           |  |

| $\odot$ | YES           | YES           |  |

By increasing N from 5 to 7,  $\eta_R$  reduces by 5.5 percentage points but the overall efficiency  $\eta_H$  improves by more than 9 percentage points, as described in Table 4.2. Since the last iteration with N=8 does not improve  $\eta_H$ , N=7 sets the optimum system design.

Finally, according to (2.4), the higher is N the lower is the value  $V_{in}$  needed to obtain the required  $V_L$ . However, by increasing N above its optimum value, only little adjustments below  $V_{th,p}$  occur on  $V_{in}$ . Thus, negligible improvements would be performed by re-designing W and  $C_P$ .

Design B, which is shown in Fig. 4.9, needs three iterations (i.e., one more than design A). Nevertheless, the final solution provides the same amount of improvement in terms of  $\eta_H$ . On the other hand, design C shows that the optimum design of the stand-alone rectifier also gives the best  $\eta_H$ , as shown in Fig. 4.10. Detailed data are reported in Table 4.3 and Table 4.4 for design B and C, respectively.

Table 4.2. Simulated antenna and rectifier PCE along with expected overall PCE within project A ( $V_L = 1.2 \text{ V}$ ,  $I_L = 1.2 \text{ }\mu\text{A}$ ).

| Iteration number | N | ηR     | ηΑ     | ηн     |

|------------------|---|--------|--------|--------|

| 1                | 5 | 46.5 % | 42.5 % | 19.8 % |

| 2                | 6 | 44.5 % | 61 %   | 27.1 % |

| 3                | 7 | 41 %   | 71 %   | 29.1 % |

| 4                | 8 | 37.5 % | 77.5 % | 29.1 % |

| 5                | - | -      | -      | -      |

Fig. 4.8. Antenna matching chart adopted in design A.

Table 4.3. Simulated antenna and rectifier PCE along with expected overall PCE within project B ( $V_L = 2.4 \text{ V}$ ,  $I_L = 600 \text{ nA}$ ).

| Iteration number | N  | $\eta_R$ | $\eta_A$ | $\eta_{\mathrm{H}}$ |

|------------------|----|----------|----------|---------------------|

| 1                | 10 | 46 %     | 45.5 %   | 20.9 %              |

| 2                | 11 | 44 %     | 56 %     | 24.6 %              |

| 3                | 12 | 42.5 %   | 64 %     | 27.2 %              |

| 4                | 13 | 41 %     | 69 %     | 28.3 %              |

| 5                | 14 | 38 %     | 74 %     | 28.1 %              |

Fig. 4.9. Antenna matching chart adopted in design B.

Table 4.4. Simulated antenna and rectifier PCE along with expected overall PCE within project C ( $V_L = 2.4 \text{ V}$ ,  $I_L = 1 \text{ }\mu\text{A}$ ).

| Iteration number | N  | $\eta_R$ | $\eta_A$ | ηн     |

|------------------|----|----------|----------|--------|

| 1                | 10 | 46.5 %   | 79 %     | 36.7 % |

| 2                | 11 | 44.5 %   | 82.5 %   | 36.7 % |

| 3                | -  | -        | -        | -      |

| 4                | -  | -        | -        | -      |

| 5                | -  | -        | -        | -      |

Fig. 4.10. Antenna matching chart adopted in design C.

### References

- [1] S. Mandal and R. Sarpeshkar, "Low-Power CMOS Rectifier Design for RFID Applications," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.54, no.6, pp.1177,1188, June 2007.

- [2] L. Grasso, R. Guerra, and G. Palmisano, "A CMOS full-wave rectifer with threshold compensation based on inherent body-voltage control," To be published in *Microwave Conference (EuMC)*, 2016 European, London, 2016.

## **Chapter V**

### Measurement methods

### 5.1 Rectifier measurement methods

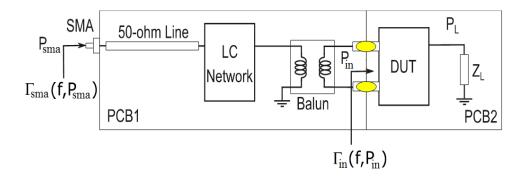

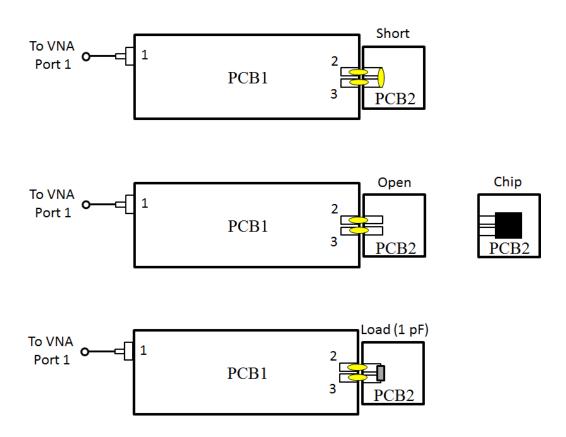

A relatively high level of input resistance is essential for the rectifier operation, especially for high sensitivity systems where  $P_{in}$  is around -20 dBm or lower. In fact, by referring to (1.6), the resulting peak voltage of  $v_{in}$  cannot be lowered at will, since the intrinsic voltage threshold of the rectifier CMOS transistors have to be guaranteed. Thus, directly characterizing the rectifier with classical 50- $\Omega$  network analyzers is extremely imprecise because of the high impedance mismatch with  $Z_{in}$ , which produces an almost complete wave reflection.

The introduction of a passive matching network between the rectifier and the 50- $\Omega$  RF generator allows delivering the proper input power  $P_{in}$  to the circuit. However, a de-embedding technique is required to determinate the effective  $Z_{in}$  value along with the correct  $\eta_R$ .

Common  $Z_{in}$  impedances require an antenna with a relatively high equivalent inductance along with low series resistance, thus resulting adequate for matching high-impedance-phase-angle chips [1]. Thus, the antenna input impedance can be expressed as

$$Z_a = R_a + j\omega L_a = Z_{in}^* \tag{5.1}$$

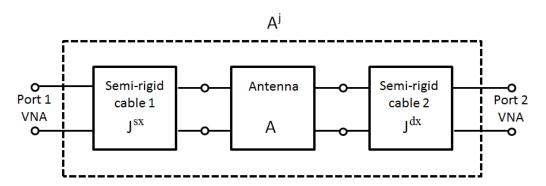

A low  $R_a$  value makes difficult to obtain a high efficiency,  $\eta_A$ . Moreover, it also requires an adequate characterization.