#### UNIVERSITA' DEGLI STUDI DI CATANIA

# Dottorato di Ricerca Internazionale in Ingegneria dei Sistemi, Energetica, Informatica e delle Telecomunicazioni XXXI ciclo

### **ALESSANDRO PARISI**

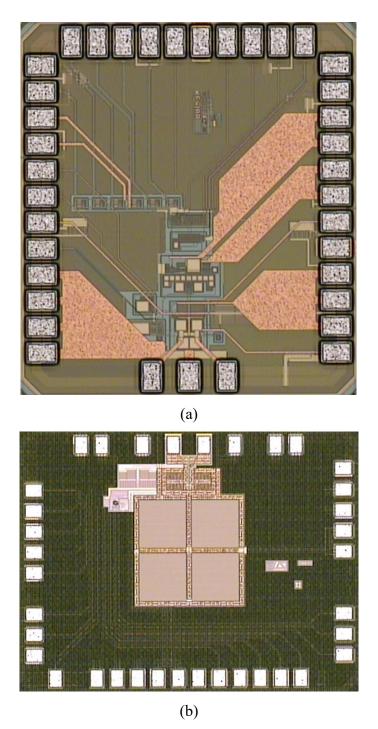

# Compact architectures for dc-dc converters with galvanic isolation

Ph.D. Thesis

**Coordinatore:**

Prof. P. ARENA

**Tutor:**

Prof. G. PALMISANO

**Co-tutor:**

Prof. E. RAGONESE

### **SUMMARY**

This thesis summarizes the main activities that I have been carried out during three years of Ph.D. studies at the RF-ADC, a joint research group between University of Catania and STMicroelectronics Catania.

Recently, galvanic isolation for both power supply and data communication is becoming mandatory in several application fields to guarantee safety and reliability, especially in harsh operative environments. A wide range of applications adopts galvanic isolation, e.g., sensor interfaces, serial link transceivers, low-power medical devices, and housekeeping power, such as gate-drivers or controllers for power converters. State-of-the-art isolators that manage both power and data transmission mainly adopt magnetic coupling by means of post-processed micro-transformers or fully integrated on-chip transformers. The galvanic isolation issue and the state-of-the-art of semiconductor isolators are presented in Chapter 1 along with the technology platforms adopted for this work, especially concerning

the implementation of galvanic isolation. It is worth noting that power and data functionalities of the proposed systems do not depend on the technology platform used for the isolation components, which can be manufactured either in post-processing technology or exploiting the SOI BCD process provided by STMicroelectronics. Therefore, this work does not address the design of the isolation transformer, but it is mainly focused on the architecture and the design of a galvanically isolated system for power and data transfer with the aim of reducing complexity and hence cost while preserving performance. Clearly, the technology platform greatly affects both efficiency and power density of the overall application.

By referring to the main limitations of the state-of-the-art solutions, this work presents three novel architectures, which implement galvanically isolated dc-dc converters with different target of applications. The main object of the proposed systems is the reduction of the number of isolated links while preserving both power and data functionalities. Chapter 2 will be focus on the design of a 100-mW galvanically isolated dc-dc converter with bidirectional data communication. The converter delivers regulated output power by means of a dedicated power link, while a second isolated channel is shared by control feedback loop and data transmission. The output voltage ranging from 2.4 V to 3.3 V and the variable output power make the proposed system very suitable for a wide range of applications. Chapter 3 will deal with a 100-mW dc-dc converter with galvanic isolation which is mainly addressed towards gate driver applications. It takes advantage of a customized architecture, which uses the isolated power link to feedback the control signal. The third isolated system will be presented in Chapter 4 and it has been designed to meet the requirements of sensor applications. The architecture is

made up of only one isolation component since power transfer, data communication and control feedback loop are implemented on the same isolated link.

Chapters 2-4 validate the functionalities and performance of the proposed systems with measurements and/or simulations, which are reported at the end of each chapter. Specifically, the dc-dc converter in Chapter 2 has been integrated and measured, so the experimental results are showed in detail. As regarding the systems in chapters 3 and 4, only simulations are provided since the exploited isolation component is under manufacturing and hence is not available for measurements. However, the active core of these systems has been integrated (see micrograph in Appendix B) and the experimental characterization will be performed as soon as possible. Finally, all the proposed architectures have been patented thus showing the industrial interest towards this Ph.D. research activity.

Besides the main topic, during my Ph.D. studies I was involved in the design of fully standard CMOS voltage references with micro- and nano-current consumption for ultra-low-power applications. Specifically, two voltage reference circuits have been designed to meet the requirements of RF-powered systems. The circuit description and measurements of these references are reported in [1] and [2].

## Content

| SUMIN   | IARY                                                        | 2           |

|---------|-------------------------------------------------------------|-------------|

| Conten  | ıt                                                          | 5           |

| List of | Tables                                                      | 9           |

| List of | Figures                                                     | 11          |

| Nomen   | clature                                                     | 17          |

| Chapte  | er 1: Galvanic isolation: definition, requisites and applic | eations. 20 |

| 1.1.    | Introduction                                                | 20          |

| 1.2.    | Safety isolation requirements                               | 23          |

| 1.3.    | Applications                                                | 30          |

| 1 3     | 3.1 Wireline networks                                       | 30          |

| 1.3.2      | 2. Current monitoring                                            |

|------------|------------------------------------------------------------------|

| 1.3.3      | 3. Gate drivers                                                  |

| 1.4.       | State-of-the-art35                                               |

| 1.4.1      | . Optocouplers                                                   |

| 1.4.2      | 2. Capacitive isolators                                          |

| 1.4.3      | 3. Magnetic isolators40                                          |

| 1.5.       | Thesis overview44                                                |

| 1.5.1      | . Technology platform46                                          |

| 1.5.2      | 2. Main results                                                  |

| Chapter    | 2: A fully integrated galvanically isolated dc-dc converter with |

| data com   | munication52                                                     |

| 2.1.       | Introduction                                                     |

| 2.2.       | System Description                                               |

| 2.3.       | Power Link                                                       |

| 2.4.       | Control/Data Link62                                              |

| 2.4.1      | . Control Link                                                   |

| 2.4.2      | 2. Data Link                                                     |

| 2.4.3      | 3. Control/Data Isolation Transformer72                          |

| 2.5.       | Experimental Results74                                           |

| Chapter    | 3: Galvanically isolated dc-dc converter exploiting a single     |

| isolated l | ink80                                                            |

| 3.1        | Introduction80                                                   |

| 3.2.     | System Description                                            | 3 |

|----------|---------------------------------------------------------------|---|

| 3.3.     | Power-Ctr Link                                                | 6 |

| 3.3.     | 1. Power Link 8                                               | 6 |

| 3.3.     | 2. Control Link                                               | 0 |

| 3.4.     | Simulation Results                                            | 1 |

| Chapter  | 4: Dc-dc converter with data communication exploiting a singl | e |

| isolated | link10                                                        | 8 |

| 4.1.     | Introduction                                                  | 8 |

| 4.2.     | System Description                                            | 0 |

| 4.3.     | Power-Data-Ctr Link                                           | 3 |

| 4.3.     | 1. Power Link                                                 | 6 |

| 4.3.     | 2. Data Link11                                                | 9 |

| 4.3.     | 3. Control Link                                               | 1 |

| 4.4.     | Simulation Results                                            | 5 |

| APPENI   | DIX A: Verilog-A models for system simulations13              | 0 |

| A.       | Introduction                                                  | 0 |

| В.       | Power link 1                                                  | 2 |

| C.       | k/EA/PWM                                                      | 3 |

| D.       | TX/RX                                                         | 5 |

| E.       | Power link 2                                                  | 6 |

| APPENI   | DIX B: Test equipment13                                       | 8 |

| APPEN   | NDIX C: Publications  | 141 |

|---------|-----------------------|-----|

| A.      | Patents               | 141 |

| B.      | Conferences           | 142 |

| C.      | Peer-reviewed journal | 143 |

| Conclu  | sion                  | 145 |

| Bibliog | raphy                 | 150 |

## **List of Tables**

| 1.1 System-level standards involving isolation by market and region [5]25                                       |

|-----------------------------------------------------------------------------------------------------------------|

| 2.1 Geometrical parameters of the power transformer58                                                           |

| 2.2 Design parameters of the power link61                                                                       |

| 2.3 Simulated efficiency breakdown of the power link ( $P_{ISO} = 100 \text{ mW}$ , $V_{ISO} = 3.3 \text{ V}$ ) |

| 2.4. Geometrical parameters of the control/data transformer                                                     |

| 2.5 Summarized performance and comparison with the state-of-the-art79                                           |

| 3.1 Geometrical parameters of the power/ctr transformer88                                                       |

| 3.2 Design parameters of the power link89                                                                       |

| 3.3 Design parameters of the PLL98                                                                              |

|        |                  |               | consumption         |                 |                     |     |

|--------|------------------|---------------|---------------------|-----------------|---------------------|-----|

| 4.1 Ge | cometrical parai | neters of the | power/data/ctr tra  | nsform          | er                  | 118 |

| 4.2 De | esign parameter  | s of the pow  | er link             | • • • • • • • • | • • • • • • • • • • | 118 |

| 4.3 Si | mulated current  | consumptio    | n of the control lo | op              |                     | 125 |

| C.1 Su | ımmarized perf   | ormance of t  | the proposed syste  | ms              |                     | 148 |

# **List of Figures**

| Fig. 1.1. Simplified block-diagram of a galvanically isolated system   | 21   |

|------------------------------------------------------------------------|------|

| Fig. 1.2. Galvanic isolation application fields.                       | 22   |

| Fig. 1.3. Physiological effects of electricity.                        | 24   |

| Fig. 1.4. Isolation levels and main additional features                | 26   |

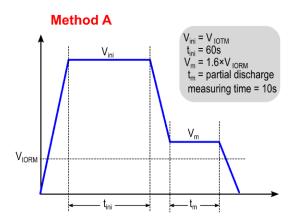

| Fig. 1.5. Simplified Method A test profile.                            | 28   |

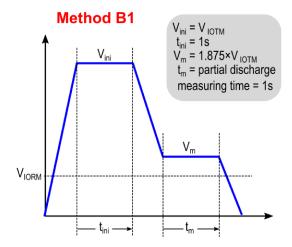

| Fig. 1.6. Simplified Method B1 test profile.                           | 28   |

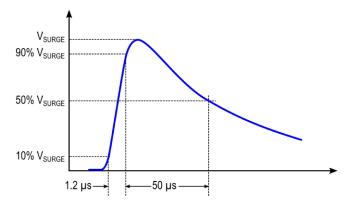

| Fig. 1.7. Simplified surge test profile                                | 29   |

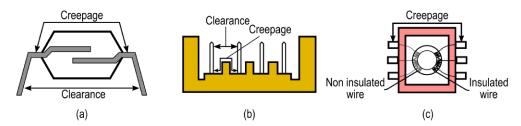

| Fig. 1.8. Definition of clearance and creepage [3]: (a) optoisolator,  | (b)  |

| connector, (c) transformer.                                            | 29   |

| Fig. 1.9. Ground loops problem in wireline communication systems. With | ıout |

| (a) and with (b) a galvanic isolator.                                  | 31   |

| Fig. 1.10. Simplified current-monitoring system architecture based on the            |

|--------------------------------------------------------------------------------------|

| shunted-resistor technique                                                           |

| Fig. 1.11. Simplified half-bridge circuit                                            |

| Fig. 1.12. (a) Typical optocoupler structure and (b) X-ray cross-section. $\dots 36$ |

| Fig. 1.13. Simplified schematic of an optocoupler device                             |

| Fig. 1.14. (a) Typical capacitive isolator system with simplified cross section      |

| of the high-voltage capacitor. (b) Photo of a six-channel capacitive digital         |

| isolator                                                                             |

| Fig. 1.15. Simplified electrical scheme for power transfer system39                  |

| Fig. 1.16. Data transfer architecture for magnetic isolator systems40                |

| Fig. 1.17. iCoupler technology. (a) Cross-section. (b) Photo of a four channels      |

| digital isolator before packaging41                                                  |

| Fig. 1.18. Power transfer system architecture                                        |

| Fig. 1.19. (a) Cross-section of the isoPower technology. (b) Photo of an             |

| isolated dc-dc converter with 4 isolated data links before packaging42               |

| Fig. 1.20. (a) SEM cross-section of the 0.35-μm BCD process metal stack              |

| with thick-oxide option. (b) Photo of a 200-mW isolated power transfer               |

| system assembled on board                                                            |

| Fig. 1.21. Architectures of power and data transfer systems with galvanic            |

| isolation                                                                            |

| Fig. 1.22. Typical architecture of a power transfer system with galvanic             |

| isolation. (a) Three chips implementation; (b) two chips implementation47            |

| Fig. 1.23. Cross-section of: (a) prost-processing technology and (b) BCD             |

| back-end for galvanic isolation                                                      |

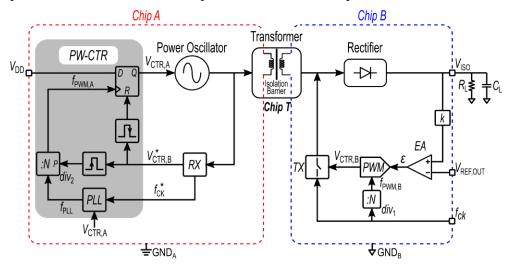

| Fig. 2.1. Basic principle of the proposed architecture                               |

| Fig. 2.2. Simplified block diagram of the dc-dc converter with bidirectional                                                    |

|---------------------------------------------------------------------------------------------------------------------------------|

| data communication                                                                                                              |

| Fig. 2.3. Power link schematic.                                                                                                 |

| Fig. 2.4. Structure of the power isolation transformer $(T_P)$                                                                  |

| Fig. 2.5. Power link simulated $V/I$ waveforms ( $P_{ISO} = 100 \text{ mW}$ , $V_{ISO} = 3.3 \text{ V}$ ).                      |

| 60                                                                                                                              |

| Fig. 2.6. Control link simplified schematics                                                                                    |

| Fig. 2.7. Simplified model of the control link for stability analysis 65                                                        |

| Fig. 2.8. Data link simplified schematics                                                                                       |

| Fig. 2.9. Simulation of HS data link in presence of 25-kV/ $\mu s$ CMT70                                                        |

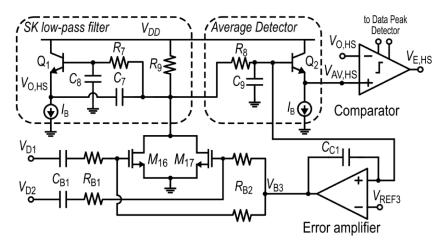

| Fig. 2.10. HS detector schematic                                                                                                |

| Fig. 2.11. LS detector schematic                                                                                                |

| Fig. 2.12. Structure of control/data transformer $T_D$                                                                          |

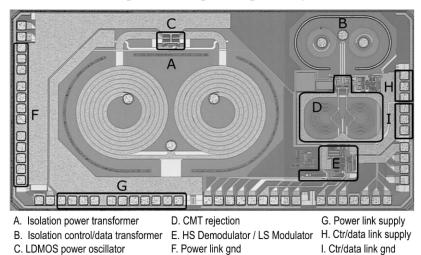

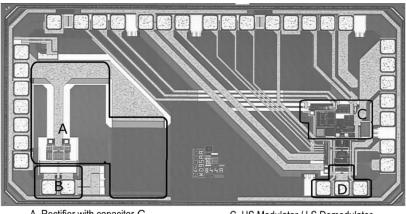

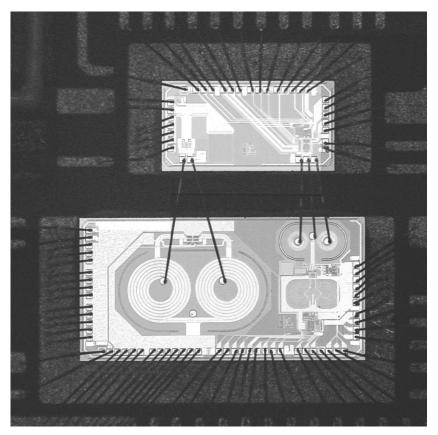

| Fig. 2.13. Micrograph of the dc-dc converter (Chip A)74                                                                         |

| Fig. 2.14. Micrograph of the dc-dc converter (Chip B)                                                                           |

| Fig. 2.15. Micrograph of the dc-dc converter assembled on board75                                                               |

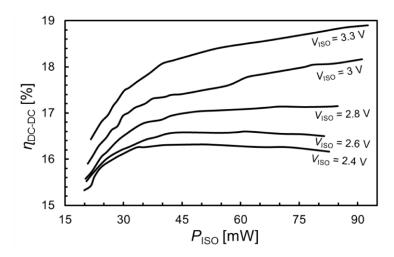

| Fig. 2.16. Power efficiency, $\eta_{DC\text{-}DC}$ , as a function of the dc output power, $P_{ISO}$                            |

| at different values of the isolated output voltage, $V_{\rm ISO}$                                                               |

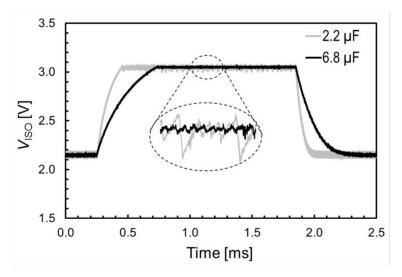

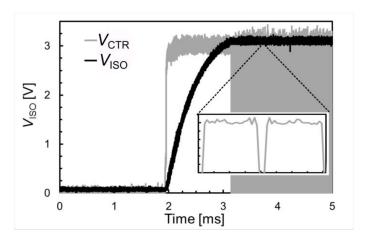

| Fig. 2.17. $V_{\rm ISO}$ transient response with two values of $C_{\rm L}$ ( $R_{\rm L}$ =110 $\Omega$ )77                      |

| Fig. 2.18. $V_{\rm ISO}$ start-up transient and corresponding PWM control signal $V_{\rm CTR}$                                  |

| $(V_{\rm REF,OUT} = 3.1 \text{ V}, f_{\rm PWM} = 100 \text{ kHz}, C_{\rm L} = 6.8  \mu\text{F}, P_{\rm ISO} = 75 \text{ mW})78$ |

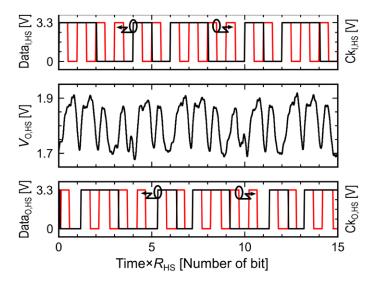

| Fig. 2.19. HS data link at maximum data rate ( $R_{\rm HS} = 50$ Mbps, $V_{\rm ISO} = 3.3$ V).                                  |

|                                                                                                                                 |

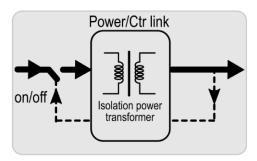

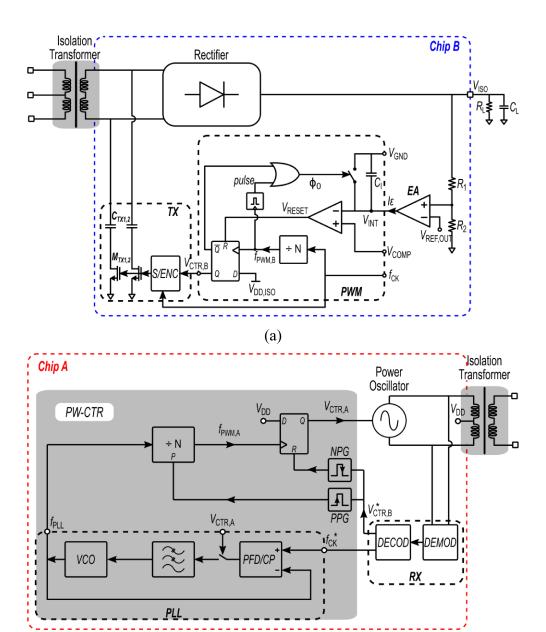

| Fig. 3.1. Architecture of a galvanically isolated dc-dc converter using a single                                                |

| isolated link81                                                                                                                 |

| Fig. 3.2. Basic principle to feedback the control signal on the same channel                  |

|-----------------------------------------------------------------------------------------------|

| of power signal82                                                                             |

| Fig. 3.3. Simplified block diagram of the dc-dc converter exploiting a single                 |

| isolated link84                                                                               |

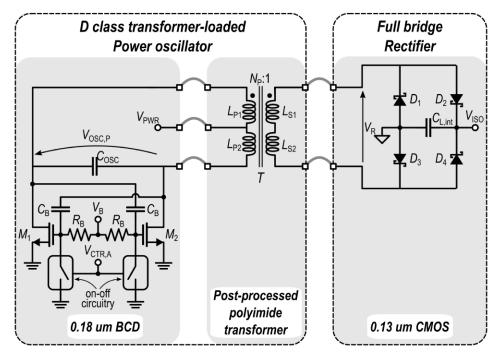

| Fig. 3.4. Schematic of the power link                                                         |

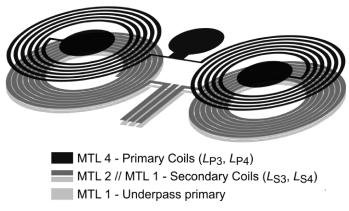

| Fig. 3.5. Structure of the power isolation transformer                                        |

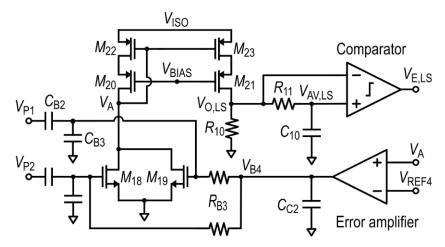

| Fig. 3.6. Control link simplified schematics: (a) Chip A and (b) Chip B 91 $$                 |

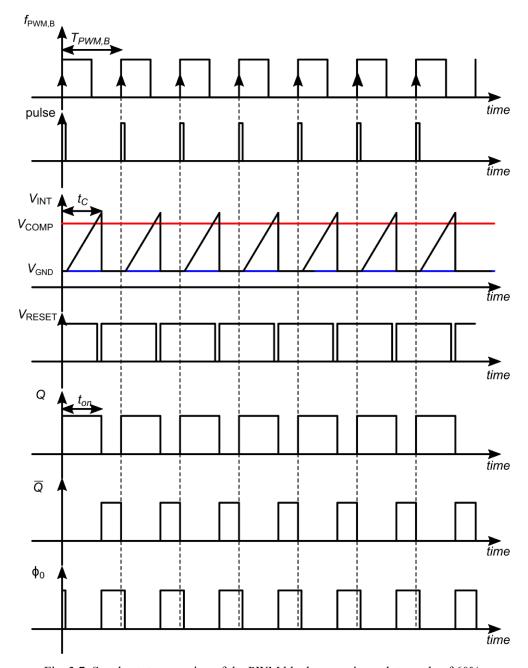

| Fig. 3.7. Steady-state operation of the PWM block supposing a duty cycle of                   |

| 60%92                                                                                         |

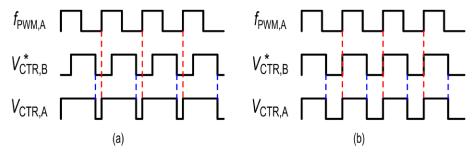

| Fig. 3.8. Time domain waveforms for reference clock, $f_{PWM,A}$ , recovered data,            |

| $V^*_{\rm CTR,B}$ and control signal $V_{\rm CTR,A}$ assuming: (a) no synchronization and (b) |

| synchronization between $f_{PWM,A}$ and $V^*_{CTR,B}$                                         |

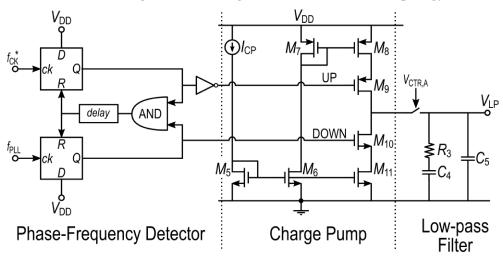

| Fig. 3.9. Schematic of the PFD/CP along with the low-pass filter95                            |

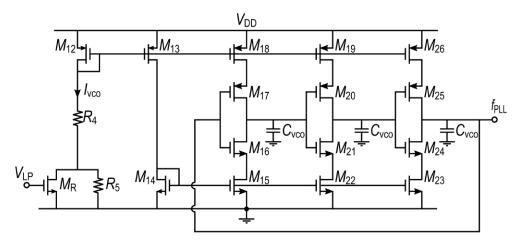

| Fig. 3.10. Schematic of the VCO.                                                              |

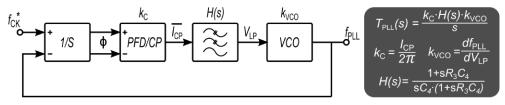

| Fig. 3.11. PLL block diagram for the loop-gain evaluation                                     |

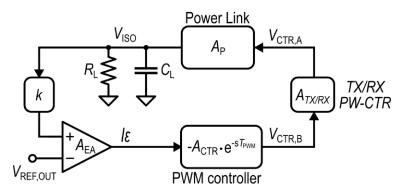

| Fig. 3.12. Simplified model of the control link for stability analysis 99                     |

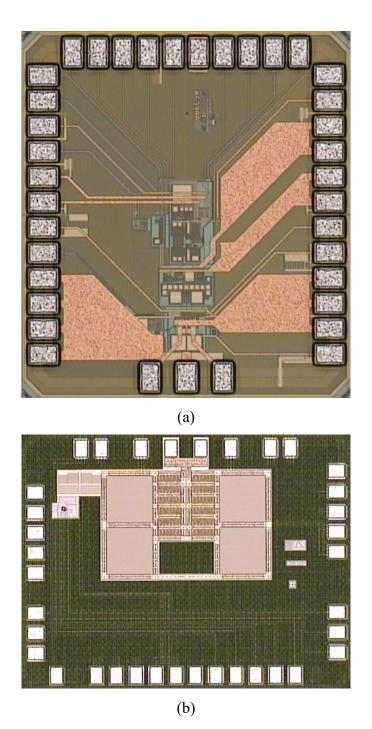

| Fig. 3.13.Micrograph of the dc-dc converter: (a) Chip A, (b) Chip B 102                       |

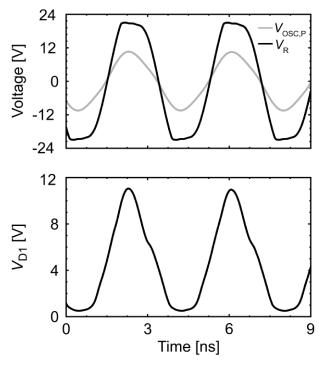

| Fig. 3.14 Power link simulated waveforms ( $P_{ISO} = 130$ mW, $V_{ISO} = 18$ V).             |

|                                                                                               |

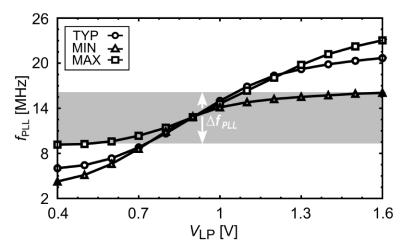

| Fig. 3.15. Simulated VCO tuning range at typical, minimum and maximum                         |

| corners. 104                                                                                  |

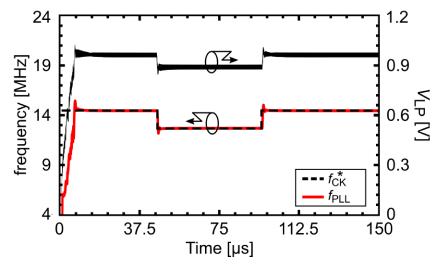

| Fig. 3.16. Transient response of the PLL to a step from 12.8 MHz to                           |

| 14.5 MHz of $f^*_{CK}$                                                                        |

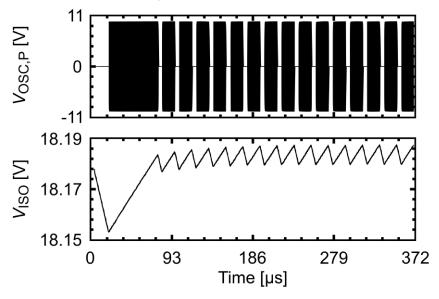

| Fig. 3.17. Power voltage oscillation at primary winding and isolated output                   |

| voltage in closed-loop condition                                                              |

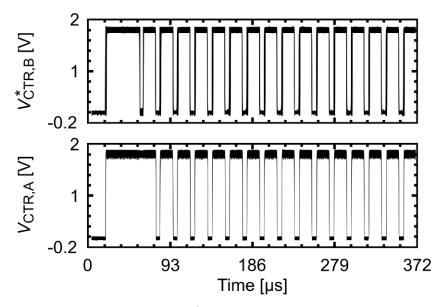

| Fig. 3.18. Recovered data $V^*_{\text{CTR,B}}$ and PWM control signal $V_{\text{CTR,A}}$      |

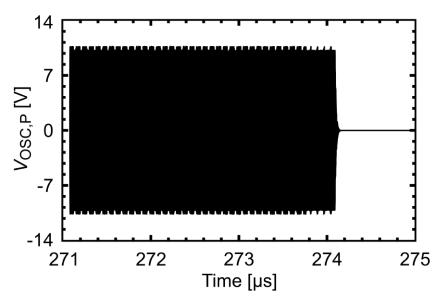

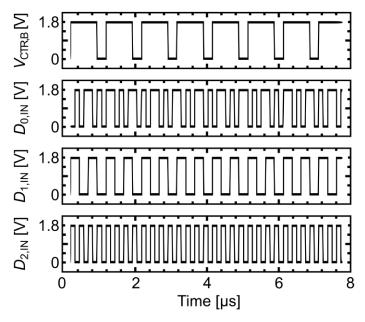

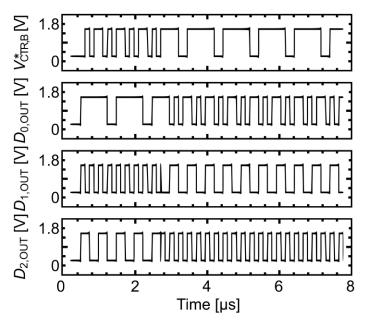

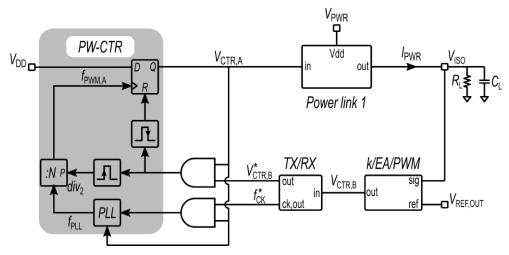

| Fig. 3.19. ASK modulation on power voltage oscillation                                  | 107            |

|-----------------------------------------------------------------------------------------|----------------|

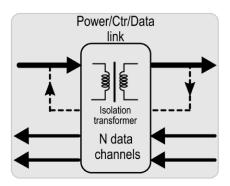

| Fig. 4.1. Architecture of a galvanically isolated dc-dc converter with                  | ı data         |

| communication using a single isolated link                                              | 109            |

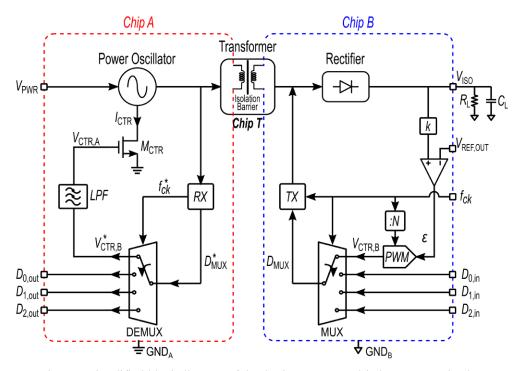

| Fig. 4.2. Simplified block diagram of the dc-dc converter with                          | data           |

| communication exploiting a single isolated link                                         | 111            |

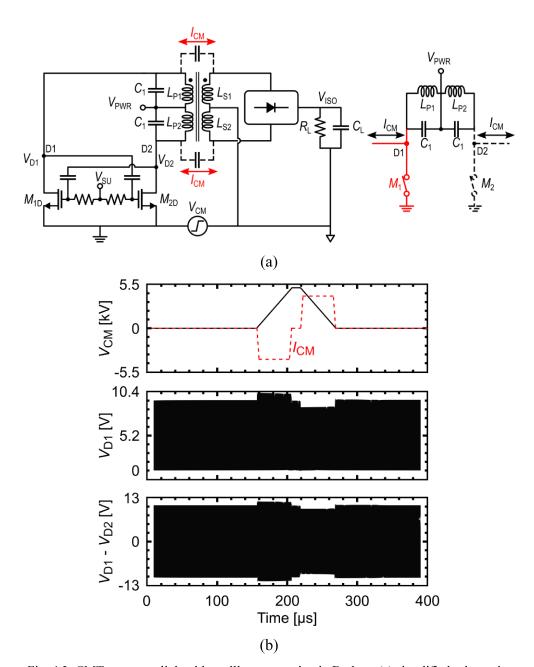

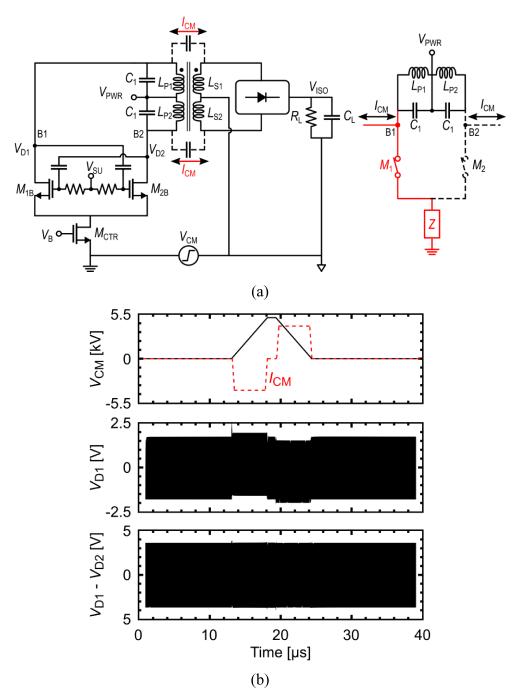

| Fig. 4.3. CMT on power link with oscillator operation in D clas                         | s: (a)         |

| simplified schematic, (b) simulated waveforms                                           | 114            |

| Fig. 4.4. CMT on power link with oscillator operation in B clas                         | s: (a)         |

| simplified schematic, (b) simulated waveforms                                           | 115            |

| Fig. 4.5. Schematic of the power link.                                                  | 117            |

| Fig. 4.6. Structure of the power isolation transformer.                                 | 118            |

| Fig. 4.7. Simplified schematic of data link with an example                             | le of          |

| synchronization.                                                                        | 120            |

| Fig. 4.8. Simplified schematic of the control link                                      | 121            |

| Fig. 4.9. Simplified model of the control link for stability analysis                   | 123            |

| Fig. 4.10. Micrograph of the dc-dc converter: (a) Chip A, (b) Chip B                    | 126            |

| Fig. 4.11. Simulated control voltage, $V_{\text{CTR,A}}$ , and isolated output voltage, | $V_{\rm ISO},$ |

| in closed-loop condition.                                                               | 127            |

| Fig. 4.12. ASK modulation on power voltage oscillation                                  | 128            |

| Fig. 4.13. Input signals of MUX.                                                        | 128            |

| Fig. 4.14. Output signals of DEMUX.                                                     | 129            |

| Fig. A.1. Model of architecture in [45].                                                | 131            |

| Fig. A.2. Model of architecture in [46].                                                | 131            |

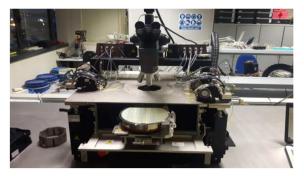

| Fig. B.1. Photograph of the experimental setup for the dc-dc conver                     | ter in         |

| Chapter 2.                                                                              | 139            |

| Fig. B.2. Cascade-Microtech probe station.                                              | 139            |

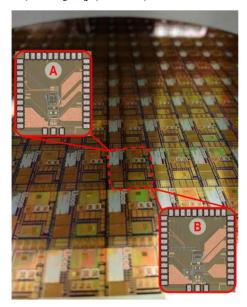

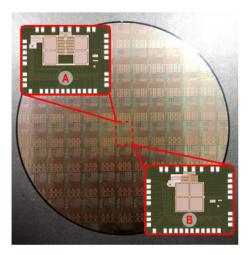

| Fig. B.3. Photograph of the silicon wafer manufactured in BCD technology  |

|---------------------------------------------------------------------------|

|                                                                           |

| Fig. B.4. Photograph of the silicon wafer manufactured in CMOS technology |

|                                                                           |

## Nomenclature

| ACRONYM | DESCRIPTION                    |  |  |  |

|---------|--------------------------------|--|--|--|

| ADC     | Analog-to-digital converter    |  |  |  |

| AGC     | Automatic gain control         |  |  |  |

| ASK     | Amplitude shift keying         |  |  |  |

| BER     | Bit error rate                 |  |  |  |

| CAN     | Controller Area Network        |  |  |  |

| CMT     | Common-mode transient          |  |  |  |

| CMTI    | Common-mode transient immunity |  |  |  |

| CSA     | Canadian Standards Association |  |  |  |

| CTR     | Current transfer ratio         |  |  |  |

| DC      | Duty cycle                     |  |  |  |

| DEMUX   | Demultiplexer                  |  |  |  |

| EA      | Error amplifier                |  |  |  |

| ACRONYM     | DESCRIPTION                               |  |  |  |

|-------------|-------------------------------------------|--|--|--|

| EM          | Electromagnetic                           |  |  |  |

| EMI         | Electromagnetic immunity                  |  |  |  |

| EN          | European Norms                            |  |  |  |

| HS          | High speed                                |  |  |  |

| HS DET      | High speed detector                       |  |  |  |

| IEC         | International Electrotechnical Commission |  |  |  |

| LDMOS       | Lateral-diffused MOS                      |  |  |  |

| LED         | Light emitting diode                      |  |  |  |

| LPF         | Low-pass filter                           |  |  |  |

| LS          | Low speed                                 |  |  |  |

| LS DET      | Low speed detector                        |  |  |  |

| MCU         | Micro-controller unit                     |  |  |  |

| Multiplexer | MUX                                       |  |  |  |

| NPG         | Negative pulse generator                  |  |  |  |

| PFD/CP      | Phase-frequency detector/charge pump      |  |  |  |

| PLL         | Phase-locked loop                         |  |  |  |

| PPG         | Positive pulse generator                  |  |  |  |

| PWM         | Pulse width modulated                     |  |  |  |

| PWM-CTR     | Power control circuit                     |  |  |  |

| PVT         | Process, voltage and temperature          |  |  |  |

| rms         | Root mean square                          |  |  |  |

| RF          | Radio frequency                           |  |  |  |

| RF-ADC      | Radio Frequency Advanced Design Center    |  |  |  |

| RX          | Receiver                                  |  |  |  |

| SC          | Switched capacitor                        |  |  |  |

| S/ENC       | Sampler/encoder                           |  |  |  |

| SEM         | Scanning electron microscope              |  |  |  |

| SiO2        | Silicon dioxide                           |  |  |  |

| ACRONYM | DESCRIPTION                            |  |  |  |

|---------|----------------------------------------|--|--|--|

| SiP     | System in Package                      |  |  |  |

| SOI BCD | Silicon on Insulator Bipolar-CMOS-DMOS |  |  |  |

|         | technology                             |  |  |  |

| TX      | Transmitter                            |  |  |  |

| UL      | Underwriters Laboratories              |  |  |  |

| UPS     | Uninterruptible power supply           |  |  |  |

| VCO     | Voltage-controlled oscillator          |  |  |  |

| VDE     | Verband Deutscher Elektringenieure     |  |  |  |

| VHF     | Very High Frequency                    |  |  |  |

## Chapter 1.

# Galvanic isolation: definition, requisites and applications

### 1.1. Introduction

This chapter introduces galvanic isolation issue and main isolation standards to be fulfilled in electronic devices, while illustrating how isolation can be implemented from a technological point of view and the applications which require isolation. Moreover, state-of-the-art solutions for both power and data transfer with galvanic isolation are reported for completeness and comparison purpose. Finally, an overview about the adopted galvanic isolation technology platforms is provided.

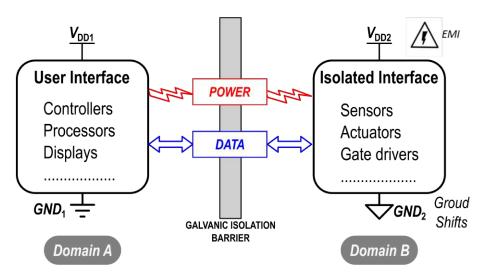

Galvanic isolation is used to separate electrically two domains while allowing at the same time an exchange of energy and/or information between them. It eliminates any direct path connections, thus preventing unwanted dc and ac current flows in both directions. A general block diagram of a galvanically isolated system is depicted in Fig. 1.1. Two domains, A and B, are isolated since one of them is subject to hazardous voltages and/or requires a different ground reference. Data signals are transferred across the galvanic isolation barrier to enable bidirectional communication between the two domains, while an isolated power supply for domain B is provided from domain A by a power transfer technique. For low-power applications, isolated power levels between 100 mW and 1 W with data rate up to 100 Mbit/s are typically required.

Fig. 1.1. Simplified block-diagram of a galvanically isolated system.

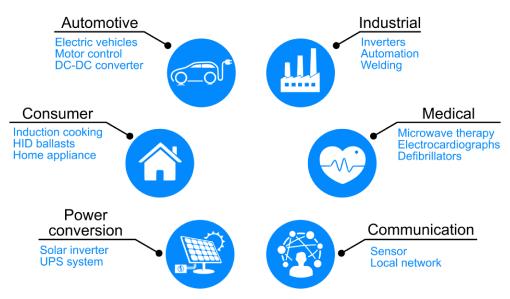

Galvanic isolation is mandatory when high power equipment is operated by human beings or to guarantee better reliability in harsh industrial environments. Galvanic isolation is also required for relatively low power levels e.g., sensor interfaces, serial link transceivers, low-power medical devices, and housekeeping power, such as gate-drivers or controllers for power converters. Fig. 1.2 summarizes the most application fields where galvanic isolation is adopted.

Fig. 1.2. Galvanic isolation application fields.

The research towards galvanic isolators has gained a lot of interest during the last decade due to the wide range of applications which need isolation either for proper operation or to meet the safety standards requirements. Several efforts have been made to increase the level of isolation while maintaining good efficiency performance. Nowadays, the research interests are addressed to the implementation of galvanic isolation by means of electromagnetic coupling, either using capacitive or inductive transfer techniques, thus replacing traditional optocoupler and discrete transformers which are expensive and bulky.

This chapter is organized as follows. Section 1.2 deals with the safety reasons of galvanic isolation while the application fields are briefly described in Section 1.3. The isolation techniques and the state-of-the-art isolators are reviewed in Section 1.4. Finally, the main outcomes of this work are summarized in Section 1.5.

## 1.2. Safety isolation requirements

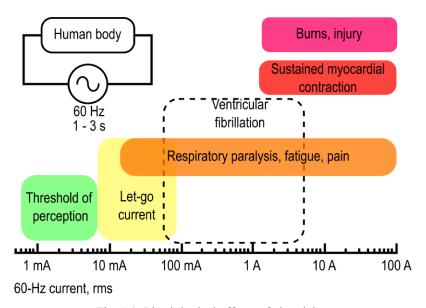

The most important motivations for providing galvanic isolation concern human safety in high voltage/current domains. Both in industrial and consumer environment, the employment of high power circuits is growing up thus leading towards several design challenges to meet safety requirements against electrical shock. Specifically, the currents, which are produced within the electronic appliances, can flow into the human body if no proper isolation is implemented, thus involving physiological effects such as involuntary movement, ventricular fibrillation or, ultimately, death [3]. Fig. 1.3 shows the range of current (expressed in rms value) which provides each effect [4]. The figure refers to a sinusoidal current source whose frequency is set at the value of 60 Hz. The electrical stimulus is applied by means of a copper cable which is held in the hands by a human being from 1 to 3 seconds. The weight of the human is about 70 kg. It can be notice that the minimum value of current that produces a slight warmth sensation is about 0.5 mA, while a current higher than 6 mA leads to the inability to *let go* (i.e., detach voluntarily from the

current source). Even higher currents determine burns, injuries and death, especially coupling them with extra-high voltages.

Fig. 1.3. Physiological effects of electricity.

The harms due to electrical shock have driven the definition of design standards and certification processes which establish the requirements for insuring human safety. Over time, national and international standards were developed. Some examples of commonly used system standards are reported in Table 1.1. System-level national regulations are defined by regional bodies, such as VDE, UL, and CSA, for Germany, United States, and Canada, respectively. Whereas international agencies such as the IEC and the EN, define the international standards. However, certification requirements can vary across the different regions of the world even when the same safety standards are referenced [5], though national and international bodies are

working to simplify the certification process, reducing the complexity caused by the high number of standards.

TABLE 1.1

SYSTEM-LEVEL STANDARDS INVOLVING ISOLATION BY MARKET AND REGION [5].

|               | Household | Informa<br>Industrial | Information | Measurement | Medical   |

|---------------|-----------|-----------------------|-------------|-------------|-----------|

|               |           |                       | technology  | and control |           |

| International | IEC 60065 | IEC 60204             | IEC 60950   | IEC         | IEC 60601 |

|               | IEC 00003 |                       |             | 61010-1     |           |

| Germany       | VDE 860   |                       | EN 60950    | VDE 410/    | VDE 0750  |

|               |           |                       |             | 0411        |           |

| USA           | UL 60065  | UL 508,               | UL 60950    | UL61010     | UL 60601  |

|               | OL 00003  | UL 60947              |             |             |           |

| Canada        |           | CSA.                  | CS A (0050  | CSA 61010 C | CSA 601   |

|               |           | 14-10                 | CSA 60950   | CSA 01010   | CSA 001   |

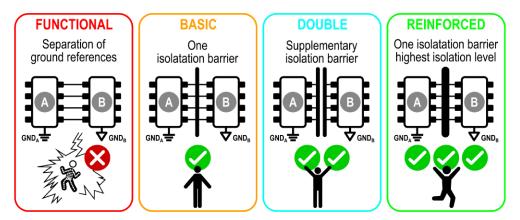

The main purpose of these standards is the definition of isolation degree in an electrical system. Commonly, the isolation levels are classified into four categories, i.e. functional, basic, double and reinforced [6]-[8], as shown in Fig. 1.4. The functional isolation consists of a simple separation of ground references which guarantees the proper operation of the system but does not provide protection against electrical shock. When safety is concerned, a galvanic barrier withstanding several kilovolts is adopted to electrically separate the user interface from the isolated interface. By using only one galvanic barrier a basic isolation is achieved. However, for a higher level of safety, a double isolation is required, which is implemented with two isolation barriers connected in series. Double isolation inherently improves the overall galvanic isolation and provides redundancy in case one of the two barriers fails. Finally, the reinforced isolation provides the highest level of isolation

available in commercial products and consists of a single isolation barrier which performs the equivalent isolation of the double level.

Fig. 1.4. Isolation levels and main additional features.

For a given application, system designers must choose the insulation characteristics of each component to meet system-level standards. The insulation specifications of a single device are defined by additional component-level standards which certify the safety requirements of the component, without guaranteeing the isolation level of the overall system. Commonly adopted component-level standards are:

- IEC 60747: Semiconductor Devices—Part 1: General

- UL 1577: Standard for Optical Isolators

- VDE 0884-10: Semiconductor Devices—Magnetic and Capacitive Coupler for Safe Isolation.

These standards provide the definition of several parameters and testing methodologies which are used to classify the isolation characteristic of the component. Specifically, the IEC 60747 and UL 1577 standards refer to the isolation specifications and testing parameters of optocoupler devices, while the VDE 0884-10 standard features the isolation requirements for highly integrated transformer-based and capacitive isolators.

The main parameters which quantify the high-voltage isolation performance and reliability of an isolator are the maximum transient isolation voltage,  $V_{\text{IOTM}}$ , the maximum repetitive voltage,  $V_{\text{IORM}}$ , and the maximum surge isolation voltage,  $V_{\text{IOSM}}$ . They are defined by the standards IEC 60747-5-5 and VDE 0884-10 and represent the isolator's capability to handle high-voltage stresses of different magnitude and transient profile without damage.  $V_{\text{IOTM}}$  is defined as the peak transient voltage that the isolator can handle without breaking down for very short periods of time, while  $V_{\rm IORM}$ is the maximum repetitive peak voltage that the isolator can withstand over a specific long time. Finally,  $V_{\rm IOSM}$  quantifies the ability of the isolator to withstand very high voltage impulses of a certain transient profile. Both  $V_{\rm IOTM}$ and  $V_{\text{IORM}}$  are measured together by means of two testing methodologies [9], Method A and Method B1, which are described by the VDE 0884-10 standard. The Method A is used during certification and its test profile is shown in Fig. 1.5. The isolator is stressed at  $V_{\text{ini}}=V_{\text{IOTM}}$  for a  $t_{\text{ini}}$  as long as 60 seconds. A following partial discharge test is carried out at a  $V_{\rm m}$  of 1.6 times  $V_{IORM}$  for a  $t_m$  of 10 seconds. On the other hand, the Method B1 is used during production manufacturing. Every device must pass this test before being released to the market. As shown in Fig. 1.6, during the process, the isolator is stressed at  $V_{\text{IOTM}}$  for only one second, with a following partial

discharge test at 1.875 times  $V_{\rm IORM}$  for one more second. Differently from Method B1, the Method A is a destructive test since high values of  $t_{\rm ini}$  and  $t_{\rm m}$  are used which compromise safety level of devices. On the other hand, the values of  $t_{\rm ini}$  and  $t_{\rm m}$  in the Method B1 are chosen to do not deteriorate the isolation capability of devices.

Fig. 1.5. Simplified Method A test profile.

Fig. 1.6. Simplified Method B1 test profile.

Fig. 1.7 depicts the surge test profile which is adopted to claim a certain  $V_{\rm IOSM}$ .

Fig. 1.7. Simplified surge test profile.

The surge test assesses the isolation level of an isolator. The basic isolation is achieved if the isolator passes the surge test at a peak voltage of 1.3 times  $V_{\rm IOSM}$ , while the reinforced isolation is certified if the isolator passes the surge test with a  $V_{\rm SURGE}$  greater than 10 kV.

It is also worth noting that isolation requires specifications on the clearance (i.e. distance through air) and creepage (i.e. distance along the surface) of the isolator's package [6], as defined in Fig. 1.8, and its fabrication materials.

Fig. 1.8. Definition of clearance and creepage [3]: (a) optoisolator, (b) connector, (c) transformer.

## 1.3. Applications

The isolation is crucial for signal integrity, system protection, and user safety, thus becoming mandatory in the wide field of applications involving digital control and measurement. This section focuses on the main low power applications of galvanic isolators which are: wireline networks, current monitoring and gate driver systems.

#### 1.3.1. Wireline networks

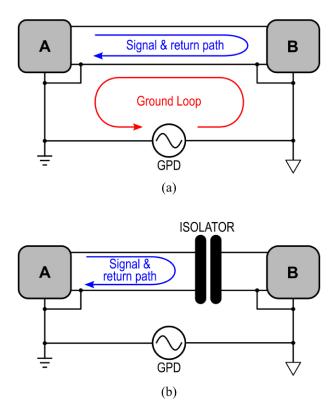

The most widespread applications of wireline networks are industrial process control, automotive, power supply regulation and point-to-point communications between computers [10]. Typically, data communication is supported by various types of physical networks, such as RS-232, RS-485, and the CAN. The main drawbacks of these networks are signal distortion and data loss due to the ground potential difference which can be established between the nodes of the networks. For instance, in RS-485 networks [11] the distances between the interconnected systems can reach up to 4000 meters thus leading to different ground references for each node. Fig. 1.9(a) shows a common situation in wireline networks. A ground loop exists between two devices (A and B) that are interconnected to exchange power and/or information. There are multiple ground paths which act as a large loop antenna and can induce currents into the system by picking up noise from the environment [12]. Moreover, ground shifts can occur in B (or A) thus causing overvoltage in A (or B) and consequently damage to the system. These problems are avoided by means of an isolator which breaks the ground loop, as shown in Fig. 1.9(b).

Fig. 1.9. Ground loops problem in wireline communication systems. Without (a) and with (b) a galvanic isolator.

The common supply voltage of low-power wireline transceivers for RS-232, RS-485 and CAN bus networks ranges from 3.3 to 5 V along with a current consumption up to tens milliamps [13]-[15]. Therefore, an isolated power supply providing around few tens of milliwatts of output power, working with supply voltages from 3.3 to 5 V is highly desirable to simplify wireline network's design.

#### 1.3.2. Current monitoring

The measurement of current flow is required in a wide range of applications, such as hybrid electrical vehicles, electrical vehicles [16] and

power line monitoring. In such systems galvanic isolation is mandatory to provide safety both in automotive and domestic environments.

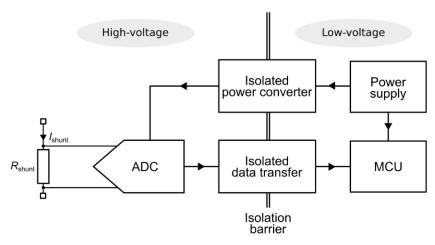

Fig. 1.10 shows the simplified architecture of a current monitoring system [17] which is based on a resistor  $R_{\text{shunt}}$  of few hundreds micro-ohms to measure current flows up to hundreds of amps. Specifically, the Ohm's law is exploited to indirectly measure the values of current by means of the measurement of the voltage across the resistor.

Fig. 1.10. Simplified current-monitoring system architecture based on the shunted-resistor technique.

By referring to Fig. 1.3, the user interface must be separated from measurement side since the current levels to be measured can involve lethal effects on human beings. Therefore, an isolation barrier is exploited to provide the separation between low voltage and high voltage sides. Moreover, an analog-to-digital converter is typically used on the high voltage side to send digital data information across the galvanic isolation barrier. The supply power for the ADC and the other circuits on the isolated side is provided by

an isolated dc-dc converter, while a digital data isolator performs data transmission from ADC (i.e., high voltage side) to the micro-controller unit (i.e., low voltage isolated side). The power consumption of the ADC is about few milliwatts thus requiring a low power dc-dc converter, while the specifications for the digital data isolator are related to data communication speed which depends on the specific application.

#### 1.3.3. Gate drivers

Renewable energy sources have gained a lot of interest in the last years due to their *green* impact on the environment. Clean alternatives, such as photovoltaic plants and wind turbines entail power conversion systems that can handle power from hundreds of watts to several kilowatts. Therefore, human safety and protection of low power circuits are essential in these applications [18].

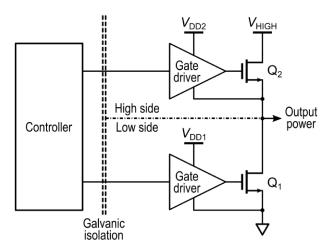

Switched-mode power electronics is the common technique which is adopted in modern power conversion systems since it achieves high efficiency both for power conditioning and control. An example of power conversion system is the gate driver for motor control. Fig. 1.11 shows a simplified architecture for motor drive applications which exploit a half-bridge topology for the N-type power switches [19]. Power MOSFET and IGBT-based inverters transform a rectified input voltage into a variable frequency voltage that drives a motor. The gate drivers are the interface between the controller and the power stage. They minimize conduction loss and switching time of the power switching devices, while avoiding destructive conditions that occur when both devices,  $Q_1$  and  $Q_2$ , are conducting at the same time.

Fig. 1.11. Simplified half-bridge circuit.

The supply voltages for the gate drivers on the low-side and high-side are  $V_{\rm DD1}$  and  $V_{\rm DD2}$ , respectively. It can be noticed that the value of  $V_{\rm DD2}$  must be very close to the ones of  $V_{\rm HIGH}$  for proper operation of the power switch  $Q_2$ . In such a condition, boost capacitors technique is typically exploited but it poses limitations on the start-up, the duty cycle, and the maximum off time for the high-side switches of the converter. while latch-up on the low-side gate-driver can occur during inductive spikes or free-wheeling diode conduction. These limitations and the risk of latch-up can be eliminated by providing to each gate driver an auxiliary galvanically-isolated supply voltage, while connecting each gate driver's ground to the source of the corresponding power switch. As a result, galvanic isolation is provided not only between controller and gate drivers but also between the low-side and high-side.

The main applications of gate driver are 600/1200V inverters, UPS equipment, solar inverters, and motor drivers in hybrid and electric vehicles [20], [21]. Common IGBTs can require a gate charge of about hundred

nano-coulombs and a voltage swing higher than 6 V [22]. According to such specification a galvanically-isolated dc-dc converter with an output power of few hundreds of milliwatts with an output voltage higher than 6 V can be exploited as auxiliary power supply for isolated gate drivers.

### 1.4. State-of-the-art

Traditionally, galvanic isolation is provided by means of optocouplers and discrete transformers which allow data transmission and power transfer, respectively. Actually, research interests are addressed towards the miniaturization of galvanic isolators, both in academic and industrial environments. The main reason is the implementation of less bulky and expansive systems than the aforementioned traditional solutions.

Galvanically isolated silicon-integrated data transmission systems have been proposed in [23]-[26], which exploit RF links [23] or capacitive [24] and magnetic coupling [25], [26] to provide galvanic isolation. The magnetic approach is also used to implement power transfer across a galvanic barrier since it provides a more efficient solution than the capacitive ones. Consequently, isolation transformer is becoming the most promising solution for the implementation of galvanic isolation since it allows both power and data transfer. Recently, several efforts have been made to improve the integration level of the inductive components by means of post-processing devices [27] (i.e., micro-transformers) or directly on silicon wafer [28]-[30] (i.e., on-chip transformer). This section provides an overview of galvanic isolators throughout the past years, from the traditional optocouplers to the most recent micro and on-chip transformers.

# 1.4.1. Optocouplers

The optocouplers were introduced at the end of 1970s and provide the highest level of galvanic isolation in data transfer systems. The data communication between the two isolated interfaces is performed by converting electrical signal to light, typically near the infrared region.

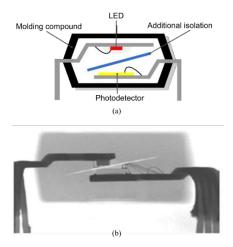

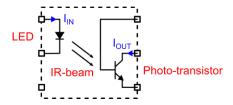

Fig. 1.12(a) and Fig. 1.12(b) depict the internal structure of an optocoupler and the x-ray scan of a device [31], respectively.

Fig. 1.12. (a) Typical optocoupler structure and (b) X-ray cross-section.

The architecture of an optocoupler is made up of an infrared light emitting diode and a photo-sensitive device (photodetector). The LED converts analog or digital signals to light which is detected by the photodetector. The latter recover data signals by re-converting the light to electrical signals. Both LED and photodetector are placed on two different metal frames which are separated by a physical gap depending on the isolation rating of the device. This gap can contain one or more additional transparent isolation layers to

improve isolation performance while reducing input-output coupling capacitance [32]. Finally, a plastic package enclosures the overall structure thus shielding from external light source and mechanical stresses.

Fig. 1.13 shows the common equivalent circuit of an optocoupler. The speed of data transmission depends on the bandwidth of the device and is related to the biasing current. Typically, data rates of about ten megabits/s require a biasing current of ten milliamps. The input current,  $I_{IN}$ , is required to turn on the LED, while the output current,  $I_{OUT}$ , is provided by the photo-transistor when the light is detected. The ratio between  $I_{IN}$  and  $I_{OUT}$  defines the current transfer ratio. It can be noticed that CTR depends on the photo-transistor current gain which is affected by variability due to biasing current, temperature and process variations. These dependencies are accentuated by the aging degradation of the LED brightness, which is accelerated by the high working current level of the device. This leads to a trade-off between performance and lifetime of optocouplers, which makes more complex their design.

Fig. 1.13. Simplified schematic of an optocoupler device.

### 1.4.2. Capacitive isolators

Capacitive isolators rely on high-voltage capacitors to sustain the required voltage rating and provide isolation. Although advanced technologies for the

implementation of high-performance isolation capacitors have been proposed [33], the most diffused isolation approach in CMOS silicon technology exploits the inter-metal dielectric, i.e. silicon dioxide, to realize low-cost isolation capacitors that enable the mass production of fully integrated digital isolators. SiO<sub>2</sub> presents several advantages such as high dielectric strength (i.e., as high as 850 V/μm [33]) which provides high isolation performance by using thin dioxide layer. Moreover, SiO<sub>2</sub> layers are available in most silicon back-ends, thus achieving high integration level by combining CMOS devices and isolation barriers on a single die.

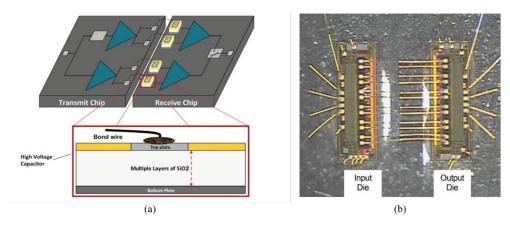

Fig. 1.14 shows a typical capacitive isolator system [34] with simplified cross section of the high voltage capacitor.

Fig. 1.14. (a) Typical capacitive isolator system with simplified cross section of the high-voltage capacitor. (b) Photo of a six-channel capacitive digital isolator.

The top and bottom plates of the capacitor are implemented by using standard metal layers, while several layers of thin-film SiO<sub>2</sub> provide the galvanic isolation. Two dice attached on separate metal frames house transmitters and receivers, respectively. The receiver chip in the figure houses

the isolation capacitor, whose top plate is connected to the transmitter output by bonding wires. Fig. 1.14(b) shows a micrograph of the isolator before packaging. Six data channels have been implemented within two chips. A great advantage of capacitive digital isolators is the low power consumption, typically only few milliamps in the state-of-the-art. In addition, a high common-mode transient immunity performance can also be achieved. These features make capacitive isolators a more reliable solution compared to optocouplers. The state-of-the-art of capacitive digital isolators includes also systems with reinforced isolation [8], which can be implemented simply by series connecting more isolation capacitors.

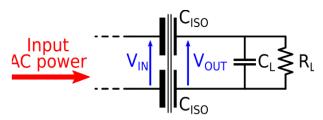

The capacitive isolators are typically adopted to implement data communication systems, while they are not suitable for power transfer applications. For instance, Fig. 1.15 shows the power transfer across the capacitive isolation barrier which is implemented by capacitors  $C_{\rm ISO}$ . Resistor  $R_{\rm L}$  and capacitor  $C_{\rm L}$  are the external load to be supplied. It can be notice that the ac input voltage,  $V_{\rm IN}$ , is highly reduced at the load level due to the capacitive partition between  $C_{\rm ISO}$  and  $C_{\rm L}$  which causes ac power loss and power efficiency degradation. The reduction of output power for a given input power is also due to the bottom plate parasitic capacitances of  $C_{\rm ISO}$  which decrease the isolation barrier efficiency.

Fig. 1.15. Simplified electrical scheme for power transfer system.

The power efficiency degradation can be limited by means of subharmonic resonant approach [35], but the isolation rating of such system is lower than the state-of-the-art results.

# 1.4.3. Magnetic isolators

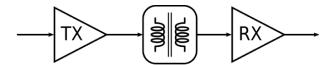

The magnetic coupling is the most suitable approach to provide galvanic isolation since it allows both power and data transfer. A typical data transfer architecture consists of a transmitter and a receiver, which exchange data information through a planar isolation transformer by using either amplitude shift keying modulated RF signals or voltage pulses. Fig. 1.16 depicts the simplified block diagram of data transfer system with magnetic isolator.

Fig. 1.16. Data transfer architecture for magnetic isolator systems.

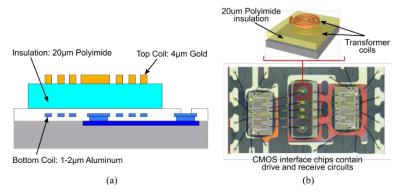

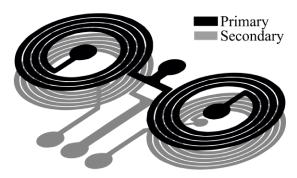

The transformer can be housed in a standalone chip or can be placed within the transmitter or receiver die, thus achieving the highest level of integration (i.e., only two chips). The first highly integrated magnetic isolators were introduced by the Analog Devices in 2001 with the iCoupler technology [36]. The iCoupler technology adopts micro-transformers realized with post processing steps to implement a multi-chip System in Package solution. A cross-section of the iCoupler technology is shown in Fig. 1.17(a). Galvanic isolation up to 5-kVrms is performed by a 20-25  $\mu$ m-thick polyimide layer, which separates the two windings of the micro-transformer. The top coil of the transformer exploits a 4  $\mu$ m-thick electroplated Au layer, while the bottom

spiral is realized on a standard IC top metal layer. A photo of a four-channel digital isolator realized with the iCoupler technology is shown in Fig. 1.17(b). State-of-the-art transformer-based digital isolators have maximum data-rate up to 6000 Mbs. Thanks to a lower parasitic capacitance between the two interfaces they also exhibit a better CMTI performance than capacitive isolators, though magnetic isolators require a more advanced technology.

Fig. 1.17. iCoupler technology. (a) Cross-section. (b) Photo of a four channels digital isolator before packaging.

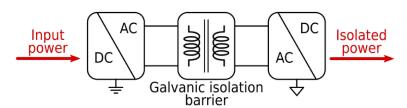

Differently from optocouplers and isolation capacitors, magnetic isolators provide an efficient solution to implement power transfer across a galvanic barrier. Fig. 1.18 shows the simplified block diagram of a power transfer system which exploits a magnetic isolator.

Fig. 1.18. Power transfer system architecture.

The key component of such a system is the transformer which provides the galvanic isolation between the two separated interfaces. Since the transformer allows the ac signals transmission while rejecting the dc component, both dc-ac and ac-dc converters are exploited to transfer power across the galvanic barrier and convert back the ac power to the dc isolated output power, respectively. The isolation transformer is typically implemented on-chip or by post-processing steps.

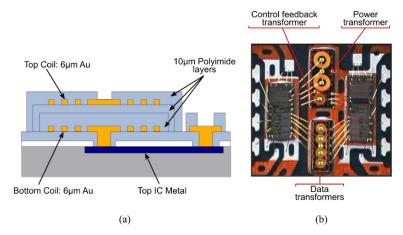

Fig. 1.19(a) depicts the cross-section of the isoPower technology [37] which has been introduced by Analog Devices to realize power micro-transformers.

Fig. 1.19. (a) Cross-section of the isoPower technology. (b) Photo of an isolated dc-dc converter with 4 isolated data links before packaging.

Both transformer's coils are implemented with thick Au metals to achieve good efficiencies. Fig. 1.19(b) shows the first multi-chip SiP dc-dc converter which combines power and data transfer capability by adding isolated data channels within the same multi-chip SiP solution. Based on this approach,

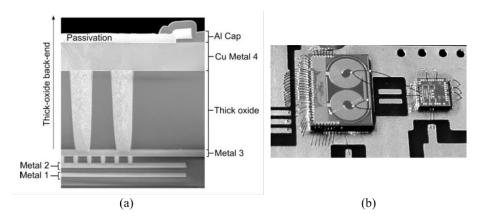

many products are available on the market [38] which deliver output power levels ranging from tens to hundreds of milliwatts, while providing separated isolated channels for data communication. Differently from the commercially available products, an interesting architecture of isolated dc-dc converter with data transmission was proposed in [39], [40]. It uses the same transformer for both data and control feedback signals thus reducing the number of isolated channels and hence the overall costs of the system. However, the best results for the reduction of the power density (i.e., the ratio between the output power and the overall area of the system) has been achieved thanks to the fully-integrated on-chip isolation transformers which have been introduced by STMicroelectronics in [41], [42]. Nowadays, only digital data isolators exploiting this technology are commercially available [20], but the power transfer feasibility was demonstrated by several fully integrated systems with power levels ranging from 20 mW to 1 W [28]-[30]. The key of this technology is the possibility to implement both active devices and isolation transformers within the same die thus leading to a two chips implementation of an isolated system. It is achieved thanks to a standard 0.35-μm-BCD process enriched with a thick-oxide module in the back-end-of-line that provides a 5-kV isolation rating between the two top metal layers thus ensuring basic isolation. The scanning electron microscope (SEM) cross-section of the four metals back-end along with the photo of a 200-mW two-chips dc-dc converter assembled on board [29] are shown in Fig. 1.20(a) and Fig. 1.20(b), respectively. Higher level of integration (i.e., only two chips) and competitive power efficiencies (i.e., from 10% to 30%) has been achieved with respect to the isolated systems which exploit isoPower technology.

Fig. 1.20. (a) SEM cross-section of the 0.35-μm BCD process metal stack with thick-oxide option. (b) Photo of a 200-mW isolated power transfer system assembled on board.

# 1.5. Thesis overview

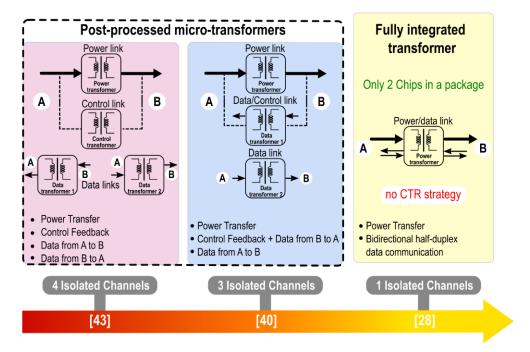

The big challenge in the design of dc-dc converters with galvanic isolation is the reduction of the number of isolated links while performing the required power and data functionalities. The main reasons can be summarized in the decreasing of both system complexity and system area occupation, with evident advantages in terms of reliability and manufacturing costs. In the last decade, several architectures of power and data transfer systems with galvanic isolation have been proposed [28], [40], [43], as shown in Fig. 1.21.

Commercially available products [43] exploit at least four isolated links which consist of:

- An isolated link for the power transmission (isolated power channel);

- An isolated link for the feedback loop of the output power control;

At least two isolated data links for bidirectional data communication (i.e., from A to B and from B to A).

Fig. 1.21. Architectures of power and data transfer systems with galvanic isolation.

The number of isolated links has been reduced from four to three channels in [40]. As mentioned in the previous section, the isolated control channel is avoided, and the control signal is multiplexed into the data bit streams which are transmitted from B to A.

Finally, the architecture in [28] implements power and data transfer by using a single isolated channel. Specifically, it exploits an ASK modulation of the power signal to perform bidirectional half-duplex data communication.

However, the output power control is not performed, and a further isolated link is required to implement the dc-dc converter functionality.

By referring to the main limitations of the state-of-the-art architectures for isolated power and data transfer, this thesis focuses on circuit and system design techniques to implement galvanically isolated dc-dc converters, with or without data communication, exploiting the minimum number of isolated links. Therefore, novel architectures which are able to perform power and data functionalities by sharing the same isolated link have been proposed during my research activity at the *RF-ADC*. It is worth noting that technology aspects regarding the implementation of galvanic isolation are not covered, since the whole technology platform was supplied and tested by STMicroelectronics.

In the next sections, the adopted technology platforms and the design procedure for both area and efficiency performance optimization will be presented. Finally, the topics of this work will be described highlighting the main results.

## 1.5.1. Technology platform

This section presents the manufacturing processes which have been exploited for the implementation of the proposed systems, with emphasis on the technology platform used for the realization of isolation components.

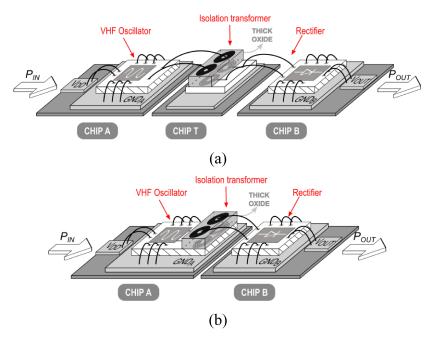

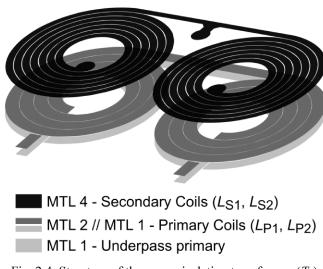

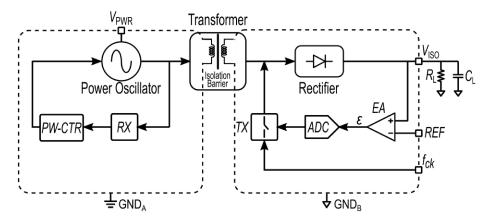

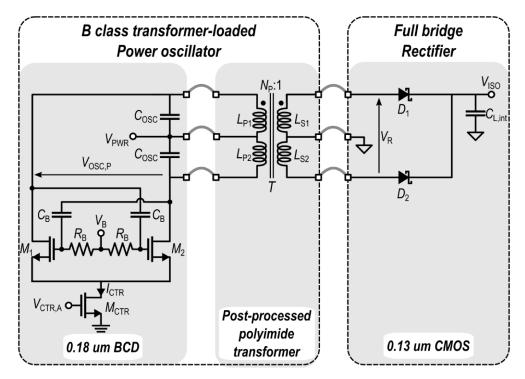

Fig. 1.22 depicts the typical architecture of a power transfer system with galvanic isolation which consists of a VHF power oscillator (i.e., the dc-ac converter), an isolation transformer (i.e., galvanic isolator) and a rectifier (i.e., the ac-dc converter). It is worth noting that the integration level of the system depends on how the transformer is implemented. Post-processing

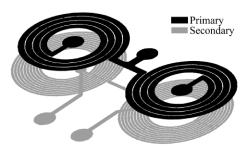

transformers achieve good efficiency performance but lead to a three chips implementation since the isolation component is manufactured in a standalone chip, i.e., chip T in Fig. 1.21(a). On the other hand, a two chips implementation can be achieved by manufacturing the isolation component on the same chip of the VHF oscillator, i.e., chip A in Fig. 1.22(b). This is obtained thanks to the BCD technology provided by STMicroelectronics.

Fig. 1.22. Typical architecture of a power transfer system with galvanic isolation. (a) Three chips implementation; (b) two chips implementation.

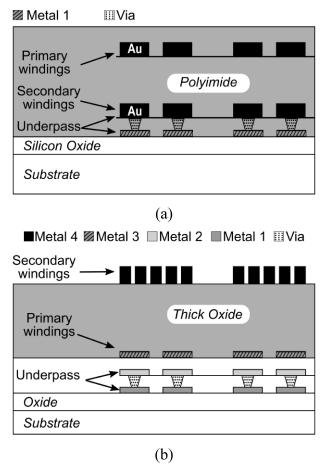

The cross-section of the adopted post-processing technology is shown Fig. 1.23(a) and consists of thick Au metal layers exploited for the transformer's coils and a polyimide layer which guarantees the galvanic isolation between primary and secondary windings. The deposition of the polyimide layer is provided by means of step-by-step processes which allow different thickness

to be implemented. Consequently, different levels of isolation (from basic to reinforce) can be achieved.

Fig. 1.23. Cross-section of: (a) prost-processing technology and (b) BCD back-end for galvanic isolation.

Finally, Fig. 1.23(b) depicts the cross-section of the 0.35-μm SOI-BCD process. This technology features both 3.3-V and 5-V CMOS transistors and several lateral-diffused MOS devices for high-voltage capabilities. Three Al metal layers with 0.45/0.55/0.9 μm thickness, respectively, and a 3.7-μm

thick top Cu layer are available for routing. The process was enriched with a thick-oxide module of several µm of thickness, which has been tested by the technology provider for a 5-kV isolation rating [42]. The primary and secondary windings of the transformer are implemented with the third and fourth metal layers, respectively, being the thick oxide located between these metals. An isolation rating of 6 kV can be also achieved by using the oxide layer between metal 3 and metal 2.

The third technology adopted in this work is a 0.13-µm standard CMOS process which provides high voltage Schottky diode with sub-GHz operation capability for the rectifier implementation.

All technologies were provided by STMicroelectronics.

#### 1.5.2. Main results

During my research activity, three novel architectures for galvanically isolated converters have been designed with different target of applications. The proposed systems overcame the main limitations of the state-of-the-art solutions concerning the implementation of more than one power and data functionalities by sharing the same isolated link, thus drastically reduce silicon area, package size and hence costs of the overall system.

Firstly, a 6-kV isolated dc-dc converter with bidirectional half-duplex data communication up to 50 Mb/s has been designed. It takes advantage of the BCD process enriched with a thick-oxide module to implement fully-integrated on-chip isolation transformers, thus achieving the highest level of integration. Indeed, the converter is made up of only two dice. Moreover, a novel control feedback loop is provided which allows data

communication to be performed on the same control channel. Therefore, only two isolated components have been exploited which are the control/data link and the power link. The latter delivers up to 93 mW output power and output voltage ranging from 2.4 V to 3.3 V thus providing an efficient solution for many applications both in medical and consumer environments.

The second system is mainly addressed to gate driver applications. It is a 100-mW step-up dc-dc converter providing around 20-V output voltage from 5-V supply voltage. The main object of this system was to perform control feedback loop on the same isolated link exploited for power transfer by means of data communication.

Finally, the third system is a galvanically dc-dc converter which has been designed to meet the requirements of sensor applications. It exploits the power link both for control feedback loop and data communication of N data channels. Therefore, it definitively provides the minimum number of isolated link while performing the required power and data functionalities which are: power transfer, data communication and control feedback loop.

It is worth noting that power and data functionalities of the proposed systems do not depend on the technology platform used for the isolation components, which can be manufactured either in post-processing steps or exploiting the SOI BCD technology. However, the technology platforms greatly affect both efficiency performance and power density.

The architecture description of the first system is presented in Chapter 2 along with experimental results which have been recently published in [44].

The second and third system are described in Chapter 3 and Chapter 4, respectively. They exploit a post-processed transformers which are under manufacturing. Therefore, simulation results have been provided for the sake

of completeness. The characterization of these two systems will be done as soon as possible. All the three architectures have been patented [45]-[47].

# Chapter 2.

# A fully integrated galvanically isolated dc-dc converter with data communication

# 2.1. Introduction

This chapter presents a fully integrated galvanically isolated dc-dc converter with data communication which exploits only two isolated links. As introduced in the first chapter, the reduction of the number of isolated links is mandatory to reduce application cost and size while maintaining all power and data functionalities. The minimum number of isolated links has been achieved by [28] in which only one isolated link is used for both power transfer and bidirectional half-duplex data communication. The main idea is

to use the isolated power channel also for a bidirectional (half-duplex) data communication by means of an ASK modulation of the power signal at the primary or the secondary windings of the isolation transformer. However, variable power functionality is not included since data communication on power channel is not compliant with an efficient power control that exploits on/off modulation (i.e., PWM modulation, Bang-Bang control scheme). Indeed, data communication requires the presence of the power signal while on/off modulation involves shutdown of the power oscillator to preserve efficiency. Moreover, considering that power and data use the same channel, important performance such maximum output power, power efficiency, data rate, and common mode transient immunity must be traded-off. Specifically, high efficiency power transfer requires large isolation power transformer which involves high parasitic capacitances between primary and secondary windings. This is against the need for a high CMT rejection.

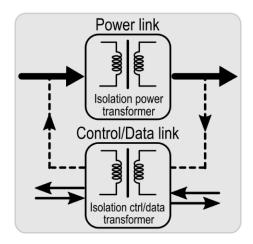

To maximize power efficiency while performing high CMT rejection on data communication, power and data must be separated and a further transformer is needed. Based on these considerations, an improvement of the architecture in [28] is proposed. Fig. 2.1 shows the block diagram of the proposed architecture. The basic principle is to use an additional isolated link to feedback the signal control for power regulation purpose. This control link is also used to perform data communication between the two isolated interfaces. In this way the power link is dedicated for power transfer only, and it can be designed to maximize system efficiency without constrains due to CMT rejection performance.

The proposed dc-dc converter delivers up to 93-mW output power with 19% maximum power efficiency and an output voltage ranging from 2.4 V to

3.3 V, while achieving a data rate up to 50 Mb/s. The variable output power control enables a large range of low-power applications, e.g. sensor interfaces requiring up to 100 mW of isolated output power.

Fig. 2.1. Basic principle of the proposed architecture.

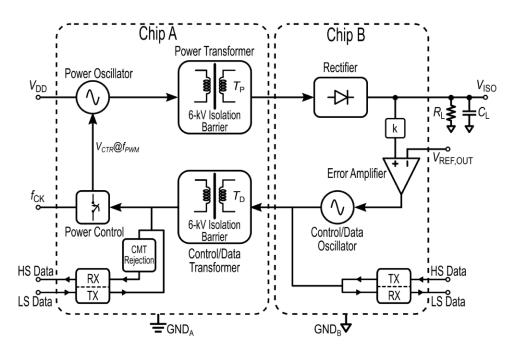

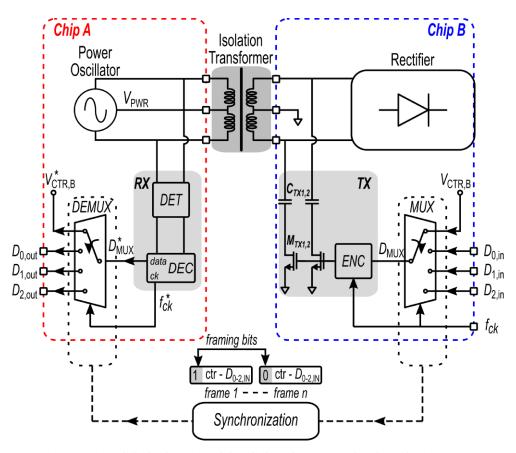

# 2.2. System Description

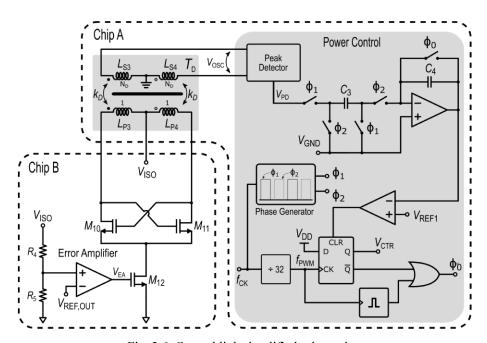

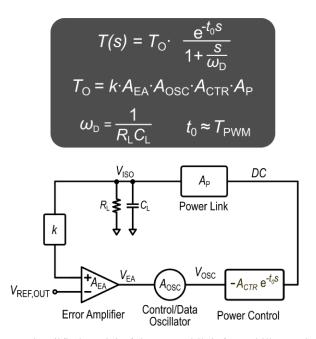

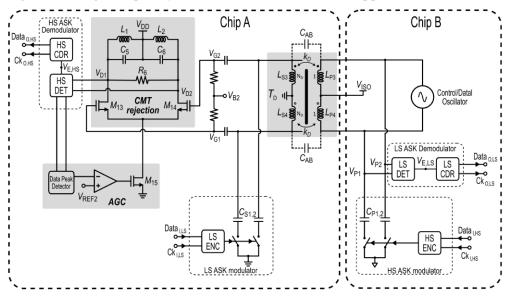

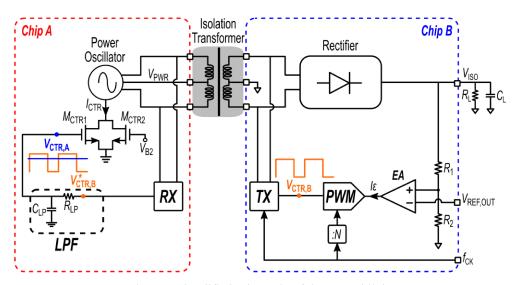

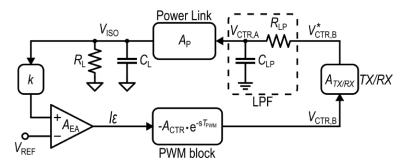

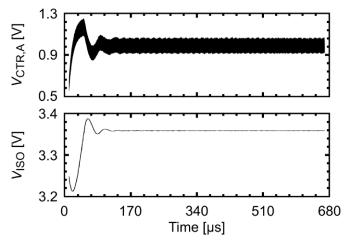

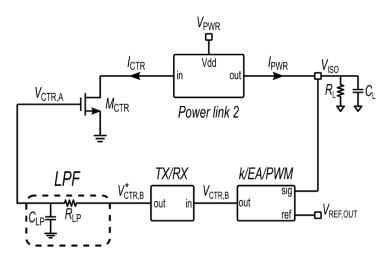

The simplified block diagram of the proposed system is depicted in Fig. 2.2. The converter is based on a novel architecture [47], which consists of a dedicated isolated link for high efficiency power transfer and an isolated signal link that is used for both output voltage/power regulation and bidirectional half duplex data communication. The dc output voltage,  $V_{\rm ISO}$ , is delivered from chip A to chip B across the galvanic barrier thanks to a power link, which is made up of a power oscillator operated at 350 MHz, an isolation transformer,  $T_{\rm P}$ , and a power rectifier. Output voltage  $V_{\rm ISO}$  is regulated in the range 2.4 V–3.3 V by means of a feedback control link that exploits a

low-power RF oscillator operated at about 900 MHz, whose oscillation amplitude changes according to the output power imposed by reference voltage  $V_{\rm REF,OUT}$  and load resistance  $R_{\rm L}$ . The galvanic isolation of the control link is guaranteed by the transformer,  $T_{\rm D}$ . The oscillation voltage of the RF oscillator is the control variable. It drives the power control block that produces a pulse width modulated signal,  $V_{\rm CTR}$ , to turn on and off the power oscillator. The frequency,  $f_{\rm PWM}$ , of control signal  $V_{\rm CTR}$  is the switching frequency of the power oscillator and can be set up to few hundreds of

Fig. 2.2. Simplified block diagram of the dc-dc converter with bidirectional data communication.

kilohertz. PWM power control preserves system power efficiency while allowing a wide range of power levels to be achieved. The control link is also exploited for bidirectional half-duplex data communication by means of amplitude modulation of the RF oscillation signal [28], [47]. High speed data stream from chip B to chip A takes advantage of the common mode transient rejection block to improve CMT immunity. A low speed data communication from chip A to chip B is also provided for those applications where configuration data are required to set chip B operation.

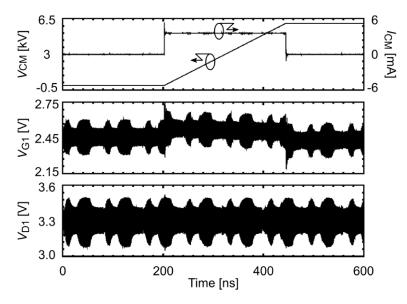

The system was fabricated in a 0.35  $\mu$ m BCD technology enriched with a galvanic isolation thick-oxide back-end provided by STMicrolectronics [41]. The thick-oxide option was used only for chip A, which includes the isolation transformers, while chip B was fabricated in a standard BCD technology. Differently from traditional galvanic isolation approaches [39], [40], [48]-[53], the transformers are completely integrated into the silicon technology and do not use post-processing steps or discrete components [28]. An isolation rating,  $BV_{AC}$ , of 5 kV is guaranteed by the oxide layer between a Cu-thick metal 4 and an Al-thin metal 3, while 6 kV isolation can be also achieved by using the oxide layer between metal 3 and metal 2. The isolation performance was previously assessed by the technology provider using several test structures [41]-[42].

# 2.3. Power Link

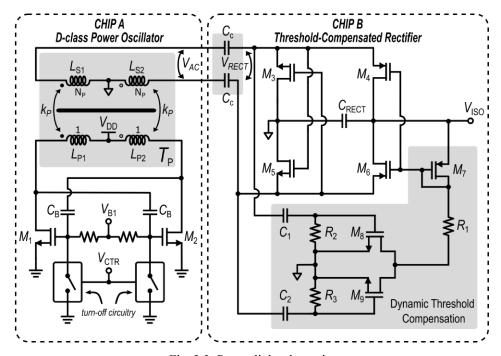

The power link is the core of the dc-dc converter and determines the efficiency performance of the overall system. It was designed to deliver a dc output power,  $P_{\rm ISO}$ , higher than 100 mW at a nominal output voltage,  $V_{\rm ISO}$ , of 3.3 V with a 3.3 V power supply,  $V_{\rm DD}$ . A simplified schematic of the power link is shown in Fig. 2.3. The architecture is made up of a transformer-based

power oscillator and a capacitive-coupled full bridge rectifier, which perform dc-ac and ac-dc conversions on chip A and chip B, respectively. Coupling capacitors  $C_{\rm C}$  are properly exploited to optimize the performance of the dc-ac conversion. The power oscillator benefits of high current/high voltage LDMOS transistors,  $M_{1,2}$ , which are operated in D class [54] thus producing an oscillation amplitude of about two times

Fig. 2.3. Power link schematic.

the supply voltage (i.e., about 7 V), which maximizes power efficiency. A capacitive partition performed by coupling capacitors  $C_B$  with the gate-source capacitances of  $M_{1,2}$  is used to set the peak value of  $V_{GS}$  and avoid gate-oxide breakdown. The on-off switches driven by PWM signal  $V_{CTR}$  allow cross-coupled pair  $M_{1,2}$  to be properly switched, thus delivering a variable

output power at constant efficiency. Isolation transformer  $T_P$ , here represented as magnetically coupled inductors, adopts a differential stacked configuration [30], as shown in Fig. 2.4. Primary ( $L_{P1,2}$ ) and secondary ( $L_{S1,2}$ ) windings are built in metal 2 and metal 4, respectively, to guarantee 6 kV galvanic isolation rating. The lower metallization layer of the process (i.e., metal 1) is exploited

Fig. 2.4. Structure of the power isolation transformer  $(T_P)$ .

TABLE 2.1

GEOMETRICAL PARAMETERS OF THE POWER TRANSFORMER.

| Parameters                        | Primary Coil     | Secondary Coil   |  |

|-----------------------------------|------------------|------------------|--|

|                                   | (half structure) | (half structure) |  |

| Number of turns ( <i>n</i> )      | 3.5              | 6.5              |  |

| Width $(w)$ [ $\mu$ m]            | 69.4             | 36.3             |  |

| Spacing (s) [µm]                  | 1                | 5                |  |

| Internal diameter $(d_{IN})$ [µm] | 300              | 300              |  |

| Outer diameter ( $d_{OUT}$ )      | 841              | 841              |  |

for the underpasses and selectively shunted to metal 2 to reduce the resistive losses of the primary winding. The geometrical parameters of half of the transformer coils are summarized in the Table 2.1. With a transformer ratio,  $N_P$ , of about 2,  $T_P$  performs a voltage step-up conversion, thus producing a peak voltage of about 12 V at the secondary winding. Finally, the oscillation voltage is properly reduced to comply with the breakdown limit of the rectifier transistors,  $M_{3-9}$  (i.e., about 5.5 V), by means of the partition between coupling capacitors  $C_C$  and the rectifier input admittance,  $Y_{RECT}$ , Therefore, such architecture performs a double conversion, i.e. a step-up followed by a step-down conversion, by means of the transformer turn's ratio,  $N_P$ , and the capacitive partition at the rectifier input, respectively. A simplified expression for the voltage gain of the power links is reported below:

$$\frac{V_{ISO}}{V_{DD}} \cong 2k_P N_P \cdot \left| \frac{4\pi j f_P C_C}{4\pi j f_P C_C + Y_{RECT}} \right| \cdot \frac{2}{\pi} \cong 1$$

(2.1)

where  $f_P$  is the power oscillation frequency,  $k_P$  is the magnetic coupling factor of  $T_P$  and  $2/\pi$  is the ideal conversion loss of the rectifier. In a standard dc-dc converter architecture (i.e., without capacitors  $C_C$ )  $N_P$  would be around unity ( $k_P \approx 0.8$ ) to guarantee an almost unitary  $V_{\rm ISO}/V_{\rm DD}$  voltage gain, thus limiting the oscillation amplitude at the drains of  $M_{1,2}$  (i.e., less than  $2V_{\rm DD}$ ) and hence reducing the oscillator core efficiency. Thanks to this step-up/step-down architecture, an improvement of the oscillator active core efficiency of about ten percentage points is achieved, which turns in an improvement of the dc-ac conversion efficiency of about five percentage points.

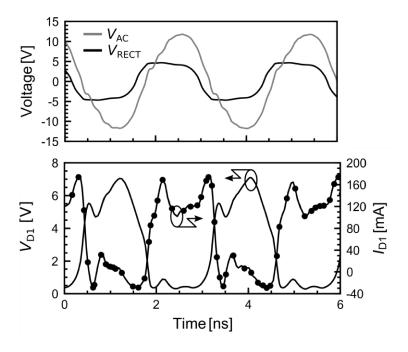

The ac-dc conversion is performed by a CMOS full bridge rectifier with a dynamic gate biasing. Indeed, transistors  $M_4$  and  $M_6$  in a full-bridge rectifier topology are diode connected or use static gate biasing. However, both approaches reduce the conversion efficiency especially at high current level. Indeed, the former is affected by the threshold voltage [28] and the latter by the reverse current on the on-chip rectifier capacitance,  $C_{RECT}$ . The proposed dynamic gate biasing overcomes these limitations since it sets the gate voltages of  $M_4$  and  $M_6$  to  $V_{ISO}$ – $V_{TH}$  only when the current flows towards the load, otherwise both  $M_4$  and  $M_6$  are turned off to prevent the flow back currents [55], thus preserving power efficiency.

The rectifier design was based on a trade-off between the conversion efficiency,  $\eta_{RECT}$ , and the reactive part of  $Y_{RECT}$  [30]. Moreover, a trade-off is also required for the oscillation frequency. Indeed, a higher oscillation

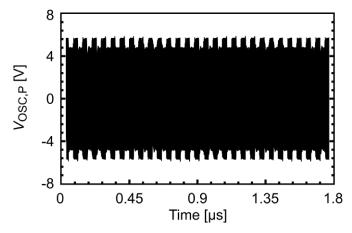

Fig. 2.5. Power link simulated V/I waveforms ( $P_{ISO} = 100 \text{ mW}$ ,  $V_{ISO} = 3.3 \text{ V}$ ).